特性

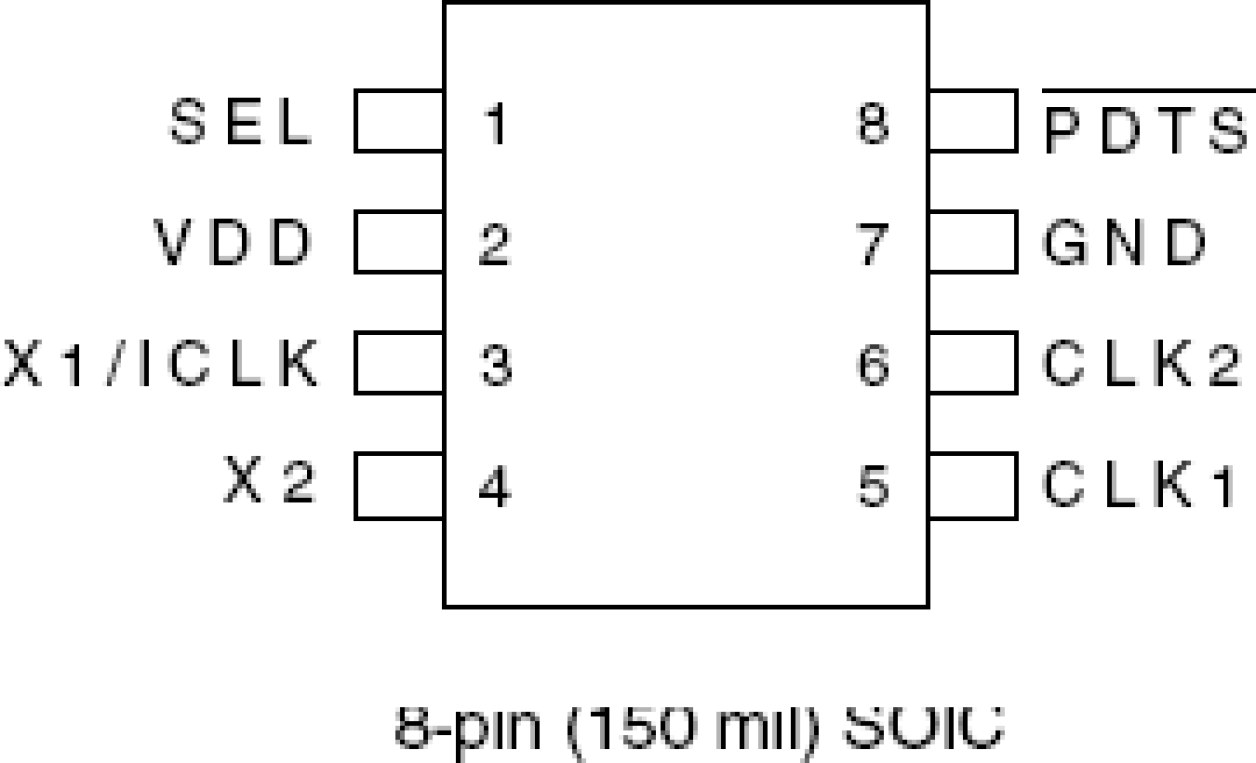

- 8-pin SOIC package – Pb-free, RoHS compliant

- Two addressable registers

- Input crystal frequency of 5 to 27 MHz

- Clock input frequency of 3 to 150 MHz

- Output clock frequencies up to 200 MHz

- Configurable Spread Spectrum Modulation

- Operating voltage of 3.3 V

- Replaces multiple crystals and oscillators

- Controllable output drive levels

- Advanced, low-power CMOS process

描述

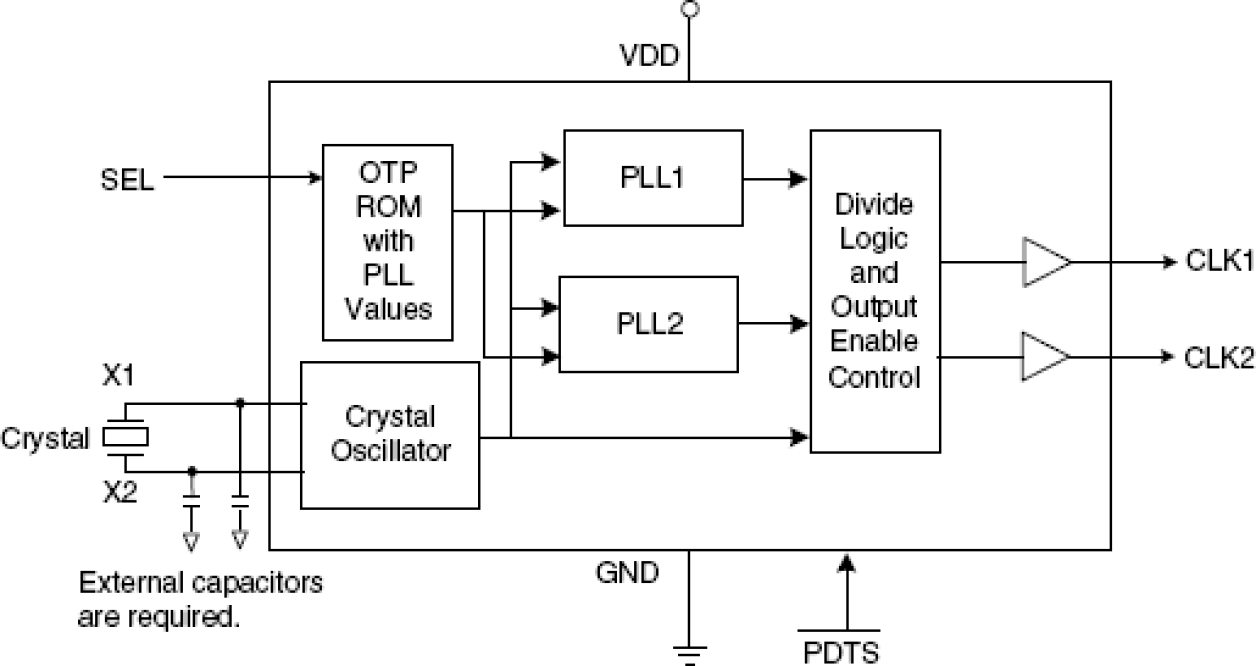

The 252 is a low cost, dual-output, field programmable clock synthesizer. The 252 can generate two output frequencies from 314 kHz to 200 MHz using up to two independently configurable PLLs. The outputs may employ Spread Spectrum techniques to reduce system electro-magnetic interference (EMI). Using IDT's VersaClock™ software to configure the PLL and output, the 252 contains a One-Time Programmable (OTP) ROM to allow field programmability. Programming features include 2 selectable configuration registers. The device employs Phase-Locked Loop (PLL) techniques to run from a standard fundamental mode, inexpensive crystal, or clock. It can replace multiple crystals and oscillators, saving board space and cost. The device also has a power-down feature that tri-states the clock outputs and turns off the PLLs when the PDTS pin is taken low. The 252 is also available in factory programmed custom versions for high-volume applications.

当前筛选条件