特性

- Host controller bus isolation from the DRAM memory during "save" and "restore" operations between DRAM and NVDIMM non-volatile memory

- AC and DC parameters optimized for DDR4, enabling the highest possible memory channel performance for NVDIMMs even when intermixed with other DIMM types

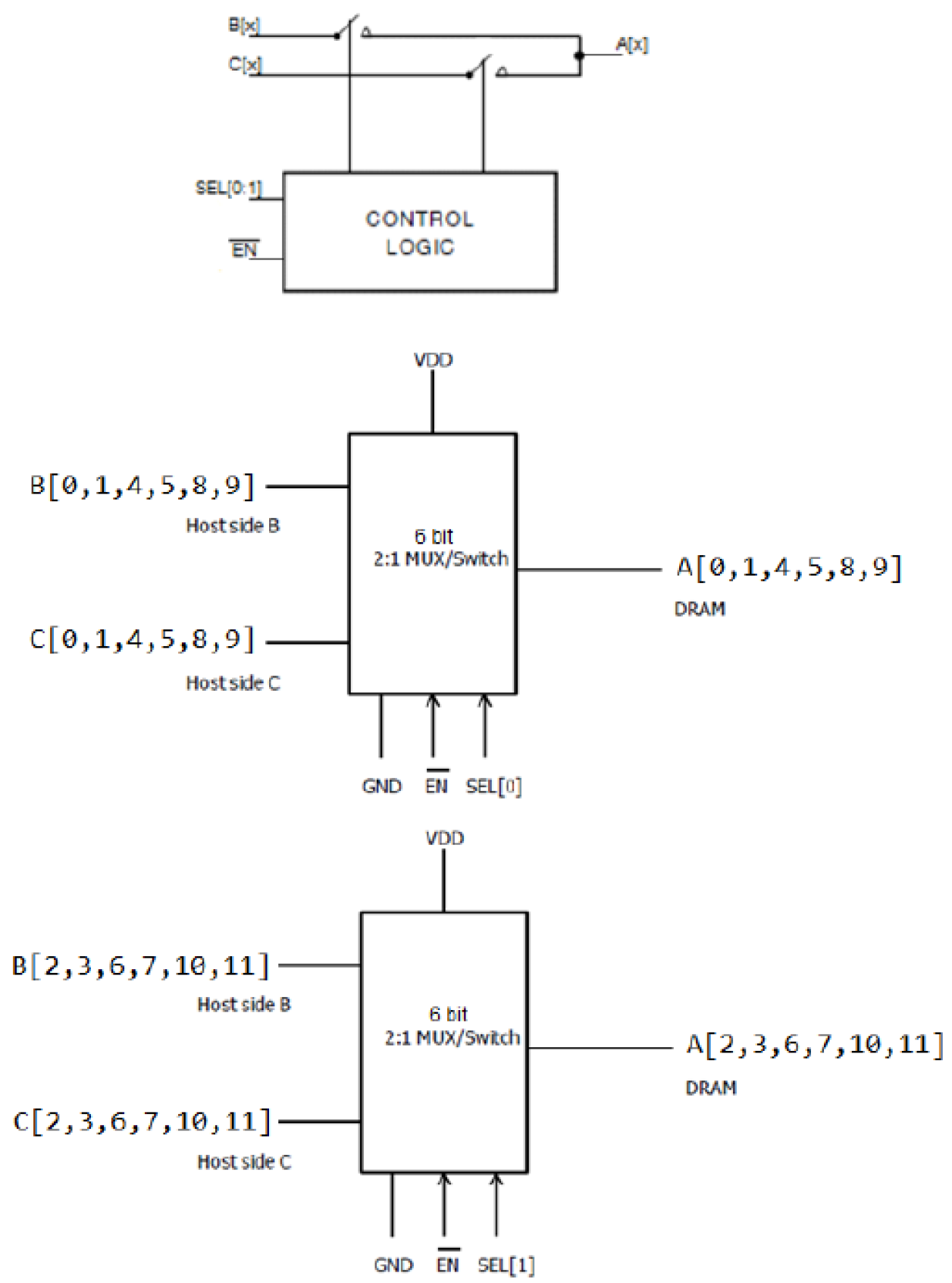

- 12-bit bus switch/multiplexer to best match the eight DQ pins and four DQS pins coming from each DRAM

- VFBGA 48-pin package for a compact footprint that can replace data buffers on the DIMM for NVMDIMM applications

- Make-before-break circuit to prevent glitches during switching operations

描述

The 4MX0121V is a 12-bit bus switch/multiplexer (MUX) designed for 2.5V supply voltage operation. The MUX is designed for operation in DDR3 and DDR4 memory bus systems. The 4MX0121V has a 1:2 switch or 2:1 multiplex topology with a 12-bit wide bus.

The 4MX0121V uses a high-speed switch architecture providing high bandwidth, low insertion loss, return loss, and very low propagation delay, allowing for the use in many applications requiring switching or multiplexing of high-speed signals.

当前筛选条件