特性

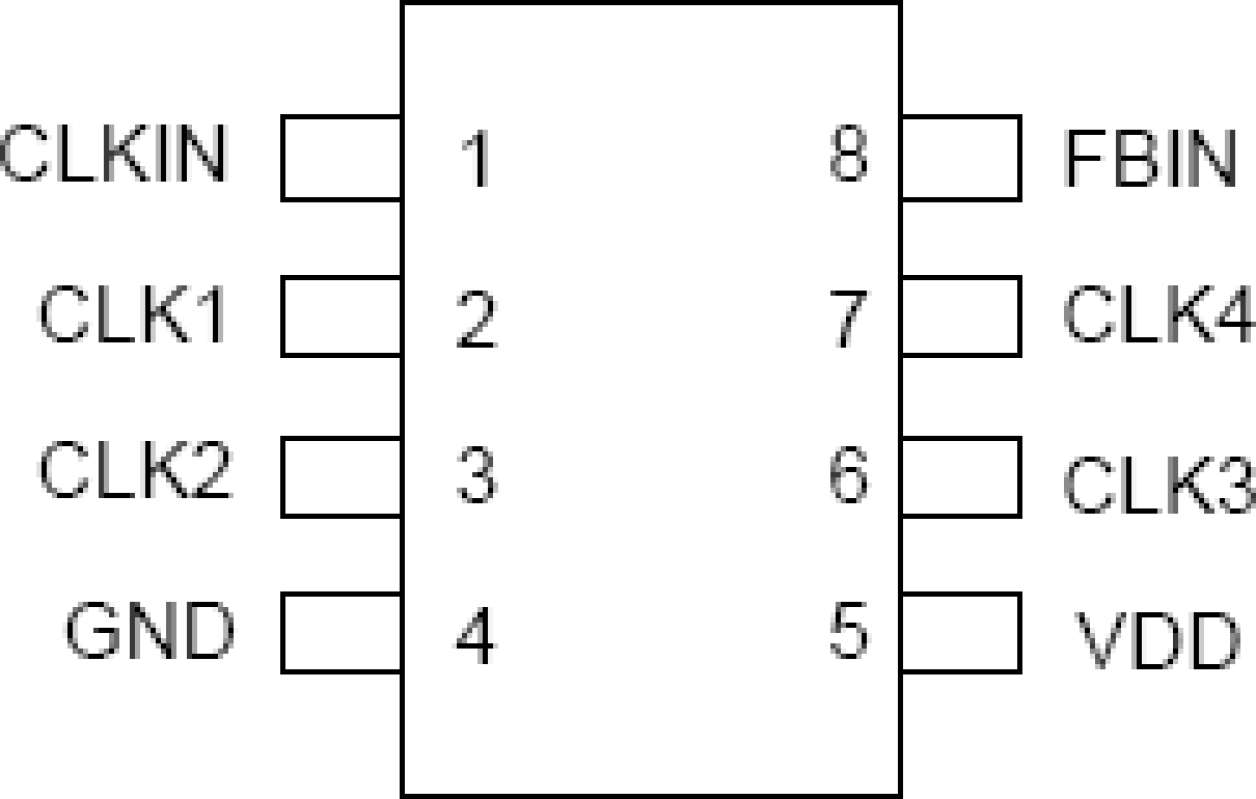

- Packaged in 8 pin narrow SOIC, Pb (lead) free

- Zero input-to-output delay

- Four 1X outputs

- Output to output skew is less than 150 ps

- Output clocks up to 160 MHz at 3.3 V

- External feedback path for output edge placement

- Spread Smart™ technology works with spread spectrum clock generators

- Full CMOS outputs with 18 mA output drive capability at TTL levels at 3.3 V

- Advanced, low power, sub-micron CMOS process

- Operating voltage from 3.0 to 5.5 V

- Industrial temperature version available

描述

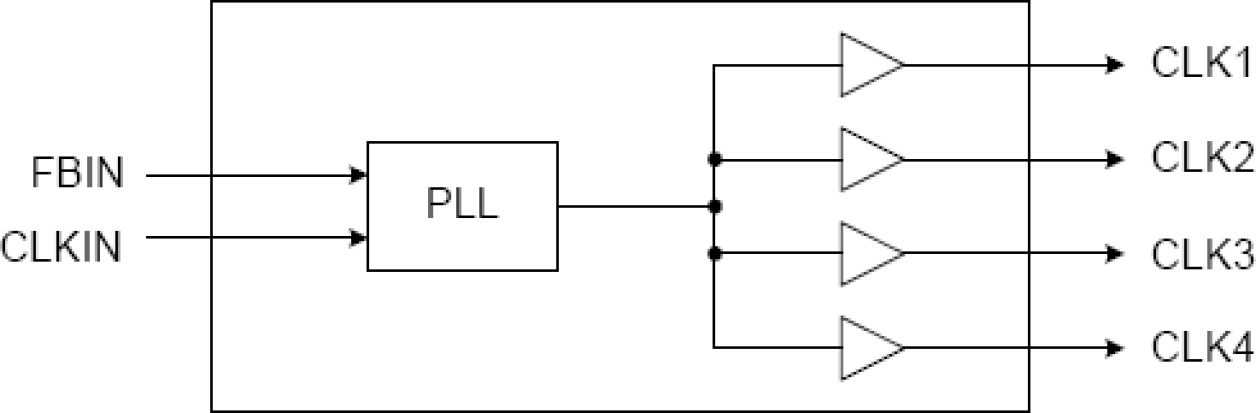

The 574 is a low jitter, low-skew, high performance PLL-based zero delay buffer for high speed applications. Based on IDT's proprietary low jitter Phase Locked Loop (PLL) techniques, the device provides four low skew outputs at speeds up to 160 MHz at 3.3 V. When one of the outputs is connected directly to FBIN, the rising edge of each output is aligned with the rising edge of the input clock. External delay elements connected in the feedback loops will cause the outputs to occur before the inputs by the amount of propagation delay of the external element.

当前筛选条件