封装信息

| Pkg. Type: | SOIC |

| Pkg. Code: | PSG24 |

| Lead Count (#): | 24 |

| Pkg. Dimensions (mm): | 15.4 x 7.6 x 2.34 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

| Moisture Sensitivity Level (MSL) | 1 |

产品属性

| Pkg. Type | SOIC |

| Lead Count (#) | 24 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tube |

| C-C Jitter Max P-P (ps) | 200 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 15 - 85 |

| Input Type | LVCMOS, LVTTL |

| Inputs (#) | 1 |

| Length (mm) | 15.4 |

| MOQ | 62 |

| Moisture Sensitivity Level (MSL) | 1 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 15 - 85 |

| Output Signaling | LVCMOS, LVTTL |

| Output Skew (ps) | 250 |

| Output Type | LVCMOS, LVTTL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 8 |

| Package Area (mm²) | 117 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 15.4 x 7.6 x 2.34 |

| Prog. Clock | No |

| Qty. per Carrier (#) | 31 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 2.34 |

| Width (mm) | 7.6 |

| 已发布 | No |

有关 5V9910A 的资源

描述

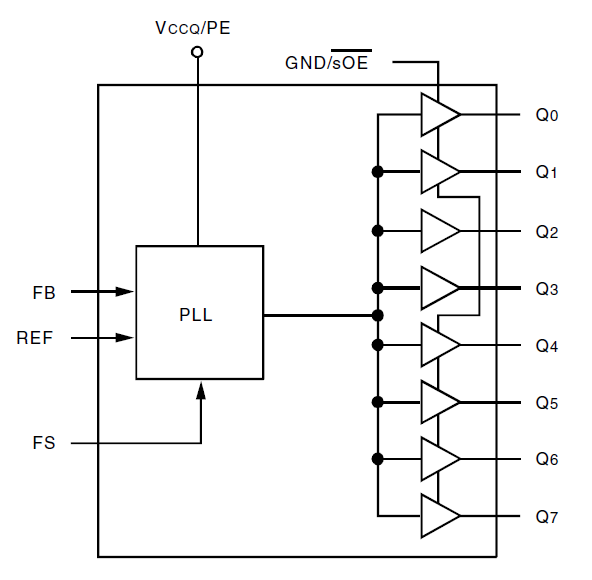

The 5V9910A is a high fanout phase locked-loop clock driver intended for high performance computing and data-communications applications. It has eight zero delay LVTTL outputs. When the GND/sOE pin is held low, all the outputs are synchronously enabled. However, if GND/sOE is held high, all the outputs except Q2 and Q3 are synchronously disabled. Furthermore, when the VCCQ/PE is held high, all the outputs are synchronized with the positive edge of the REF clock input. When VCCQ/ PE is held low, all the outputs are synchronized with the negative edge of REF. The FB signal is compared with the input REF signal at the phase detector in order to drive the VCO. Phase differences cause the VCO of the PLL to adjust upwards or downwards accordingly. An internal loop filter moderates the response of the VCO to the phase detector. The loop filter transfer function has been chosen to provide minimal jitter (or frequency variation) while still providing accurate responses to input frequency changes.