特性

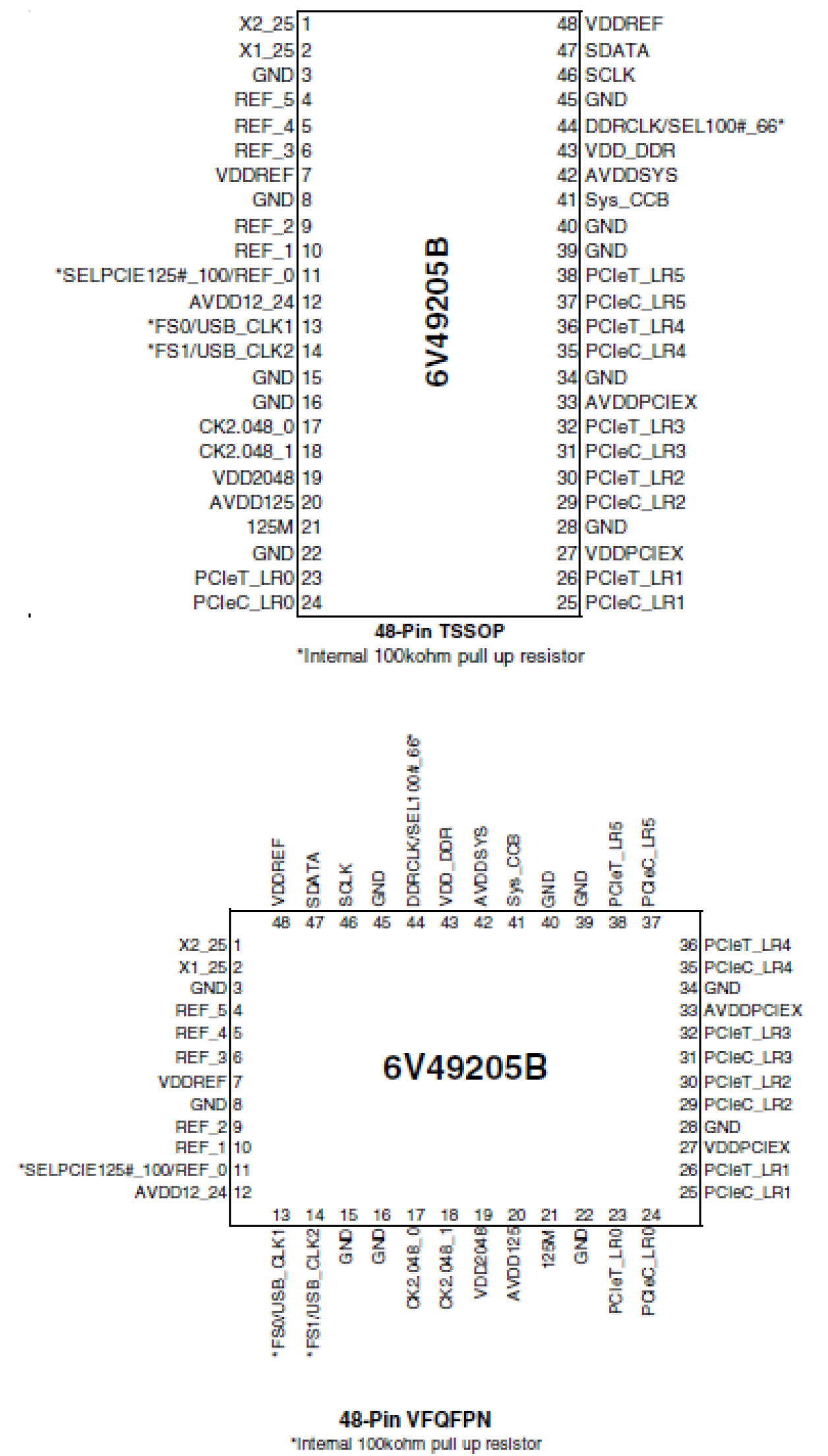

- Packaged as a 48-pin TSSOP or 48-pin VFQFPN–Pb-free, RoHS-compliant

- Replaces 11 crystals, 2 oscillators, and 3 clock synthesizers

- Uses external reference crystal

- Operating voltage – 3.3V

- Supports spread spectrum modulation

- Supports I2C Standard and Fast modes

- Meets PCI Express Gen 1/2/3 performance

- 2.048MHz output to output skew <250ps

- Low phase noise for REF outputs

- Advanced, low-power CMOS process

- Supports the industrial temperature range

描述

The 6V49205B is a clock generator specifically designed for the Freescale P1010, P1020, P2020, and P2040 processors. The device uses a low-cost 25MHz crystal as an input and generates 19 high-quality output clocks for use in Freescale-based systems. The 6V49205B produces the following output frequencies:

- 1 – 100MHz/66.66MHz/80MHz/83.333MHz selectable for System CCB

- 1 – DDR_CLK; selectable 100MHz or 66.66MHz

- 2 – 12MHz/24MHz selectable outputs for USB

- 6 – PCIe differential low-power push-pull pairs; selectable 100MHz or 125MHz

- 6 – REF, 25MHz

- 2 – 2.048MHz for E1

- 1 – 125MHz for Gigabit

产品参数

| 属性 | 值 |

|---|---|

| Output Freq Range (MHz) | 100 - 100, 66.66 - 66.66, 80 - 80, 83.333 - 83.333, 12 - 12, 24 - 24, 125 - 125, 2.048 - 2.048, 25 - 25 |

| Supply Voltage (V) | 3.3 - 3.3 |

| Output Type | LVCMOS, HCSL |

| Xtal Freq (MHz) | 25 - 25 |

| Package Area (mm²) | 49, 76.3 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 25 - 25 |

| Function | Generator |

| Input Type | Crystal, LVCMOS |

| Output Banks (#) | 8 |

| Core Voltage (V) | 3.3 |

| Output Voltage (V) | 0.8V, 3.3V |

| Product Category | General Purpose Clocks, PCI Express Clocks, Processor Clock Generators |

应用

- System clock for Freescale P10xx and P20xx-based designs

当前筛选条件