封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | PQFP |

| Pkg. Code: | DR208 |

| Lead Count (#): | 208 |

| Pkg. Dimensions (mm): | 28.0 x 28.0 x 3.5 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Pb (Lead) Free | No |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 208 |

| Pb (Lead) Free | No |

| Carrier Type | Tray |

| Architecture | BankSwitchable |

| Bus Width (bits) | 36 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 4608 |

| Function | JTAG |

| I/O Frequency (MHz) | 133 - 133 |

| I/O Type | 3.3 V LVTTL, 2.5 V LVTTL |

| Interface | Sync |

| Length (mm) | 28 |

| MOQ | 12 |

| Moisture Sensitivity Level (MSL) | 3 |

| Organization | 128K x 36 |

| Output Type | Flowthrough, Pipelined |

| Package Area (mm²) | 784 |

| Pb Free Category | e0 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 28.0 x 28.0 x 3.5 |

| Pkg. Type | PQFP |

| Qty. per Carrier (#) | 24 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 3.5 |

| Width (mm) | 28 |

| 已发布 | No |

有关 70V7599 的资源

描述

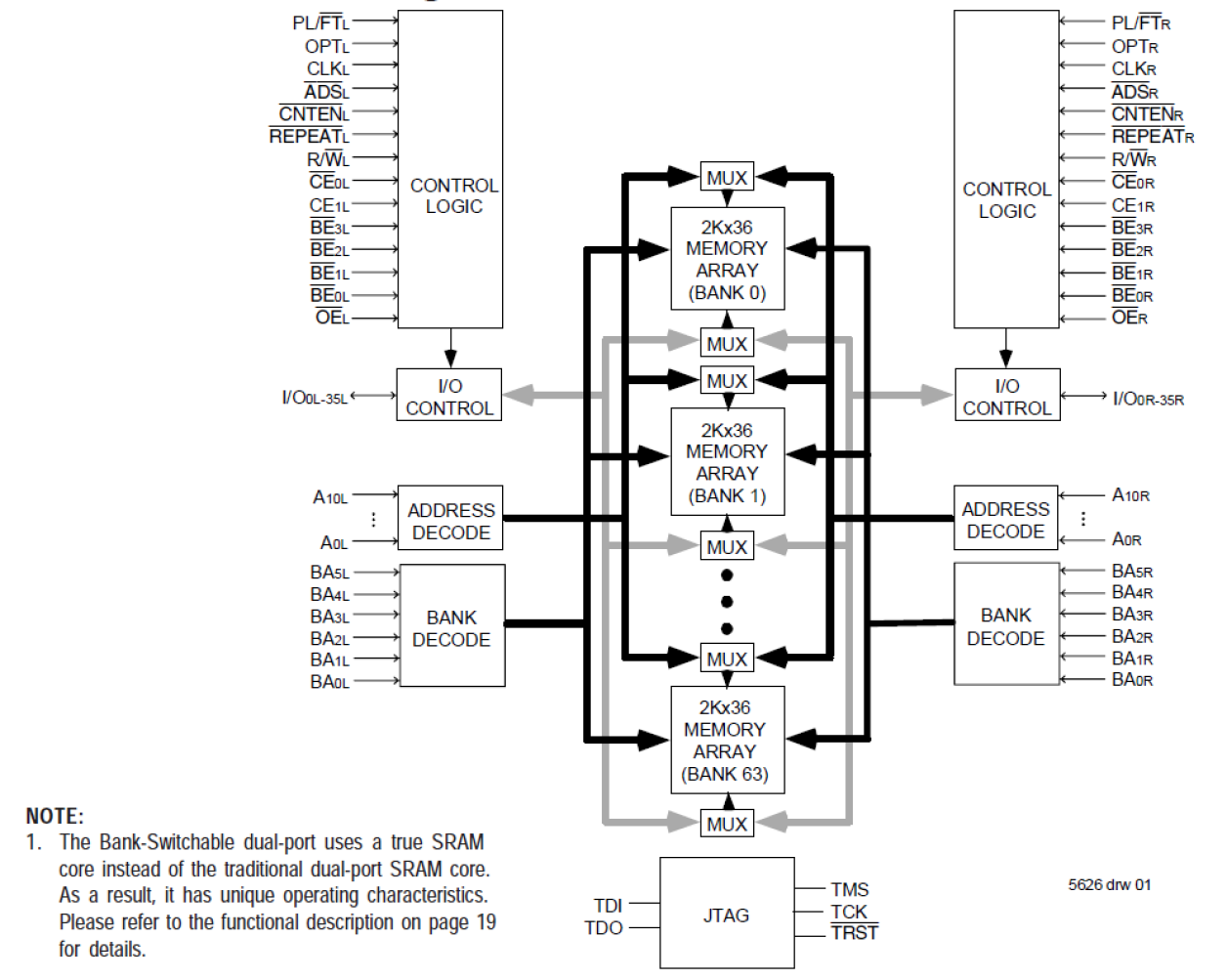

The 70V7599 is a high-speed 128K x 36 (4Mbit) synchronous Bank-Switchable Dual-Ported SRAM is organized into 64 independent 2Kx36 banks and has two independent ports with separate control, address, and I/O pins for each port, allowing each port to access any 2Kx36 memory block not already accessed by the other port. An automatic power down feature, controlled by CE0 and CE1, permits the on-chip circuitry of each port to enter a very low standby power mode.