封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PN120 |

| Lead Count (#): | 120 |

| Pkg. Dimensions (mm): | 14.0 x 14.0 x 1.4 |

| Pitch (mm): | 0.4 |

环境和出口类别

| Pb (Lead) Free | No |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 120 |

| Pb (Lead) Free | No |

| Carrier Type | Reel |

| Architecture | Bi-directional |

| Bus Width (bits) | 36 |

| Core Voltage (V) | 5 |

| Density (Kb) | 72 |

| Family Name | SyncBiFIFO |

| Function | Mailbox |

| I/O Frequency (MHz) | 83 - 83 |

| I/O Type | 5.0 V TTL |

| Interface | Synchronous |

| Length (mm) | 14 |

| MOQ | 750 |

| Moisture Sensitivity Level (MSL) | 3 |

| Organization | 1K x 36 x 2 |

| Package Area (mm²) | 196 |

| Pb Free Category | e0 |

| Pitch (mm) | 0.4 |

| Pkg. Dimensions (mm) | 14.0 x 14.0 x 1.4 |

| Pkg. Type | TQFP |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 750 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 14 |

有关 723642 的资源

描述

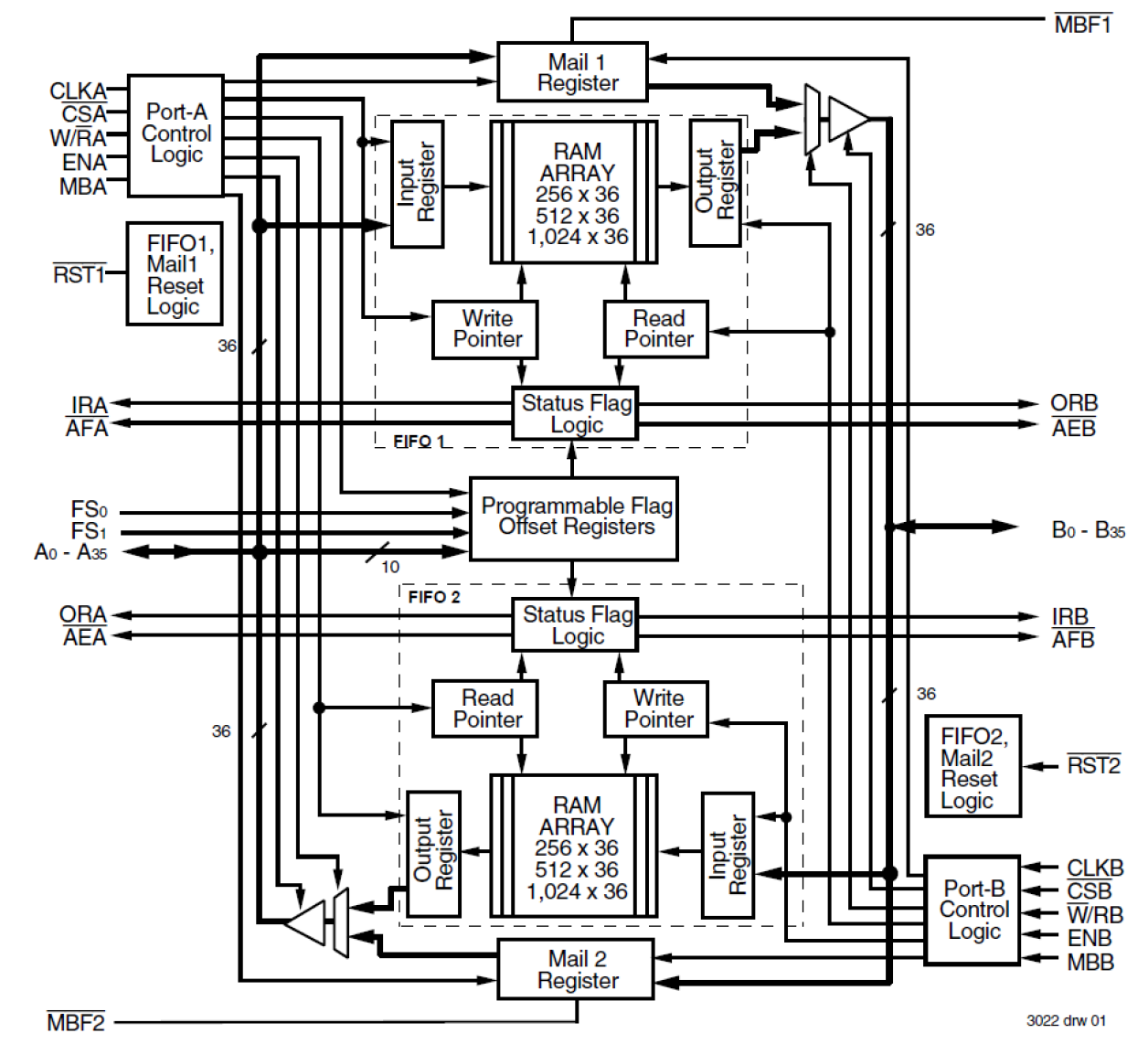

The 723642 is a monolithic Bidirectional SyncFIFO (clocked) memory. Two independent 1K x 36 dual-port SRAM FIFOs on board each chip buffer data in opposite directions. Communication between each port may bypass the FIFOs via two 36-bit mailbox registers. Each mailbox register has a flag to signal when new mail has been stored. The enables for each port are arranged to provide a simple bidirectional interface between microprocessors and/or buses with synchronous control.