特性

- A and C speeds

- High-speed, low-power CMOS

- Typical tSK(o) (output skew) < 250ps

- Low input and output leakage ≤1µA (max.)

- VCC = 5V ±10%

- Balanced output drivers of ±24mA

- Reduced system switching noise

- Typical VOLP (Output Ground Bounce) < 0.6V at VCC = 5V, TA = 25 °C

- Available in 56-pin SSOP and TSSOP packages

描述

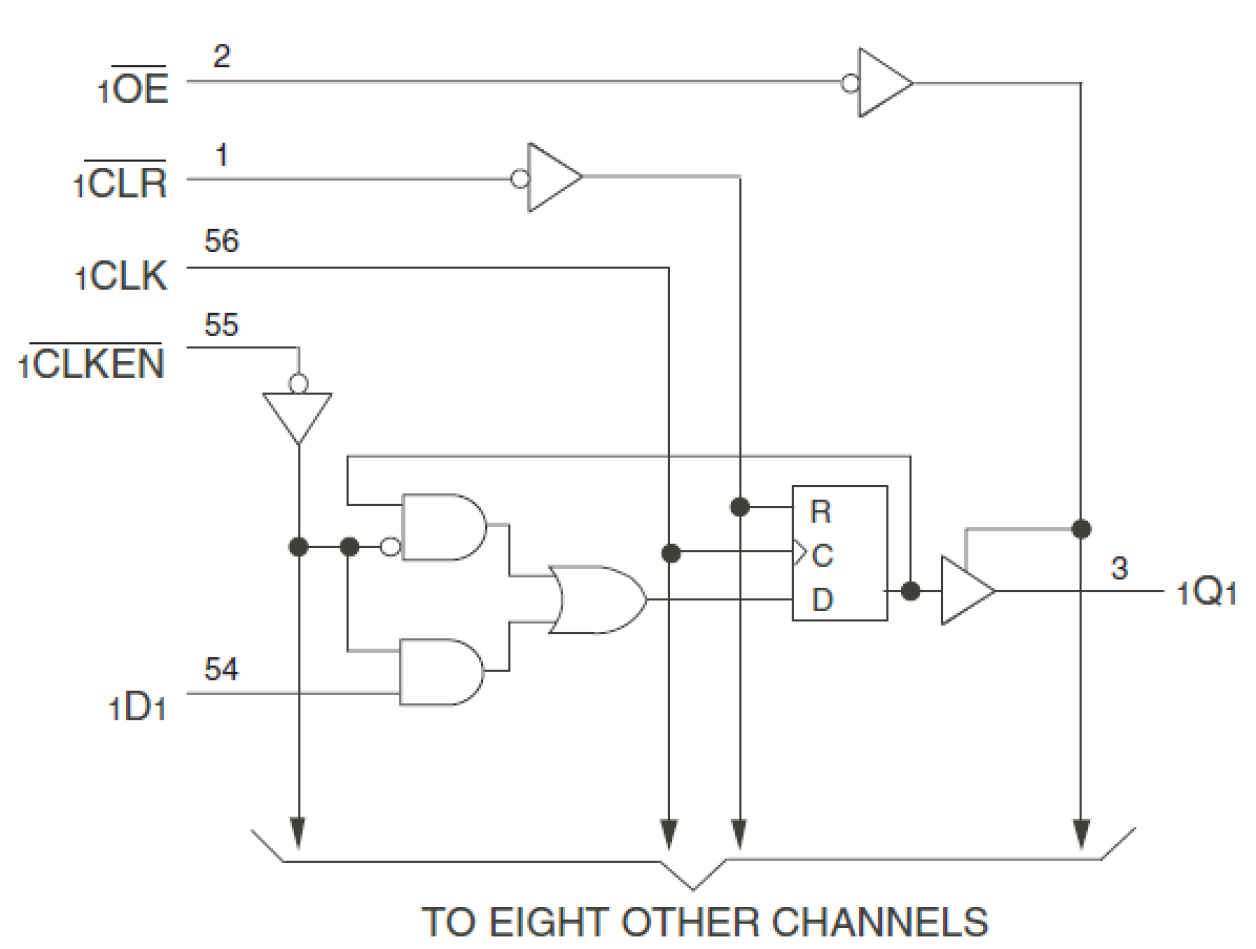

The 74FCT162823T 18-bit high-speed, low-power bus interface register with clock enable (xCLKEN) and clear (xCLR) controls are ideal for parity bus interfacing in high-performance synchronous systems. The device can operate as two 9-bit registers or one 18-bit register. The 74FCT162823T offers low ground bounce, minimal undershoot, and controlled output fall times – reducing the need for external series terminating resistors. The 74FCT162823T operates at -40 °C to +85 °C.

产品参数

| 属性 | 值 |

|---|---|

| Function | Register |

| Pkg. Code | PVG56 |

| Temp. Range (°C) | -40 to 85°C |

| Bus Width (bits) | 18 |

| Core Voltage (V) | 5 |

| Speed Grade | C |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| SSOP | 18.4 x 7.5 x 2.3 | 56 | 0.64 |

当前筛选条件