封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | PLCC |

| Pkg. Code: | PLG28 |

| Lead Count (#): | 28 |

| Pkg. Dimensions (mm): | 11.5 x 11.5 x 3.63 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 28 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 3 |

| Input Freq (MHz) | 10 - 150 |

| Output Freq Range (MHz) | 10 - 150 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 38 |

| Package Area (mm²) | 132.3 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 11.5 x 11.5 x 3.63 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Core Voltage (V) | 3.3 |

| Input Type | LVCMOS, LVTTL |

| Inputs (#) | 2 |

| Length (mm) | 11.5 |

| MOQ | 76 |

| Output Banks (#) | 4 |

| Output Signaling | LVCMOS, LVTTL |

| Output Skew (ps) | 250 |

| Output Type | LVCMOS, LVTTL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 8 |

| Pkg. Type | PLCC |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 3.63 |

| Width (mm) | 11.5 |

| 已发布 | No |

有关 74FCT388915T 的资源

描述

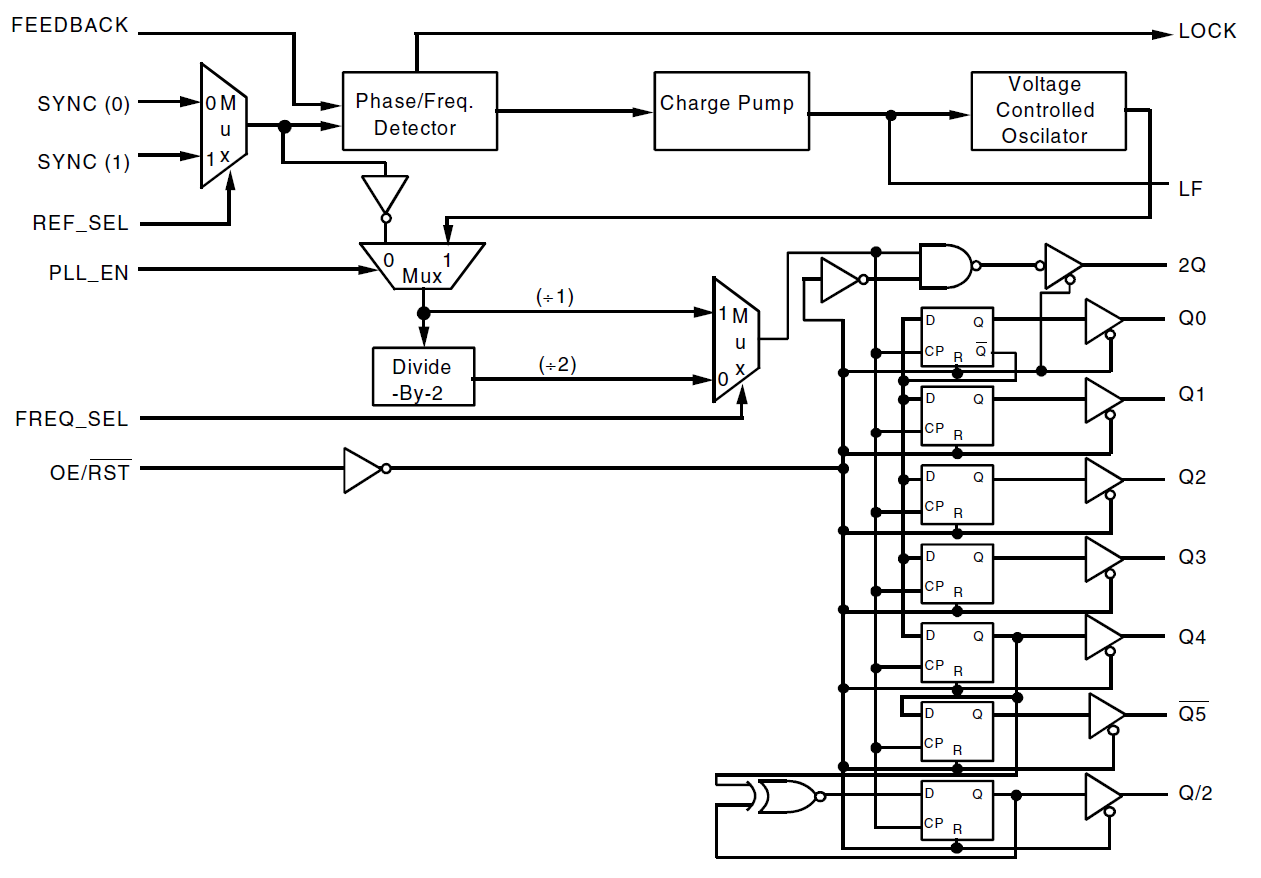

The FCT388915T uses phase-lock loop technology to lock the frequency and phase of outputs to the input reference clock. It provides low skew clock distribution for high performance PCs and workstations. One of the outputs is fed back to the PLL at the FEEDBACK input resulting in essentially zero delay across the device. The PLL consists of the phase/ frequency detector, charge pump, loop filter and VCO. The VCO is designed for a 2Q operating frequency range of 40MHz to f2Q Max. The FCT388915T provides 8 outputs, the Q5 output is inverted from the Q outputs. The 2Q runs at twice the Q frequency and Q/2 runs at half the Q frequency. The FREQ_SEL control provides an additional ÷ 2 option in the output path. PLL _EN allows bypassing of the PLL, which is useful in static test modes. When PLL_EN is low, SYNC input may be used as a test clock. In this test mode, the input frequency is not limited to the specified range and the polarity of outputs is complementary to that in normal operation (PLL_EN = 1). The LOCK output attains logic HIGH when the PLL is in steady-state phase and frequency lock. When OE/RST is low, all the outputs are put in high impedance state and registers at Q, Q and Q/2 outputs are reset. The FCT388915T requires one external loop filter component as recommended in Figure 3.