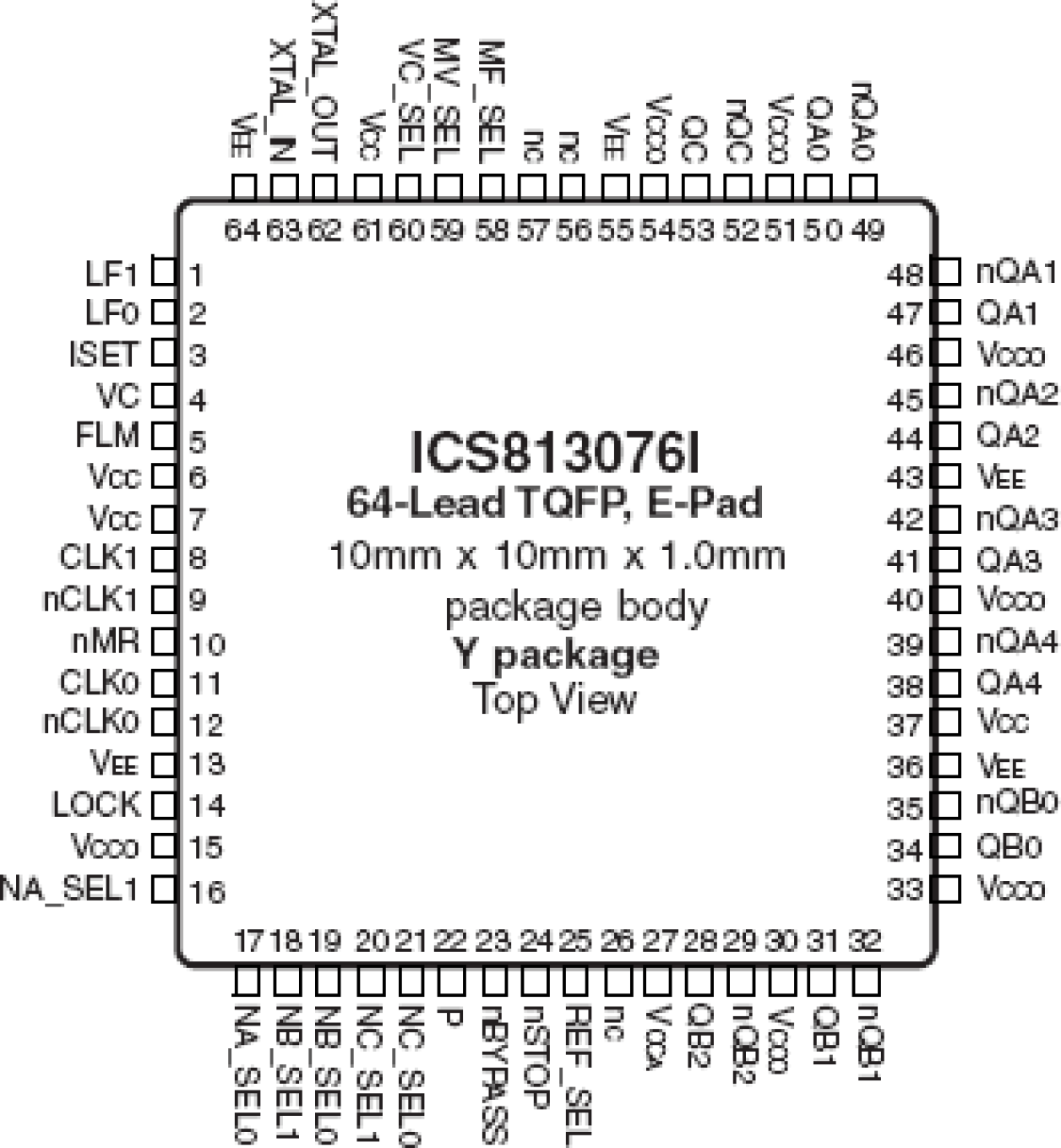

封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | EDG64 |

| Lead Count (#): | 64 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | TQFP |

| Lead Count (#) | 64 |

| Pb (Lead) Free | Yes |

| Carrier Type | Reel |

| Abs. Pull Range Min. (± PPM) | 50 |

| Advanced Features | PLL-based Synchronous Clock |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 15.36 - 15.36, 30.72 - 30.72, 61.44 - 61.44 |

| Input Type | LVPECL, LVDS, HSTL, SSTL, HCSL |

| Inputs (#) | 2 |

| Length (mm) | 10 |

| Loop Bandwidth Range (Hz) | 72 - 871 |

| MOQ | 500 |

| Moisture Sensitivity Level (MSL) | 3 |

| Output Banks (#) | 3 |

| Output Freq Range (MHz) | 24.576 - 24.576, 30.72 - 30.72, 98.304 - 98.304, 122.88 - 122.88, 153.6 - 153.6, 491.52 - 491.52, 614.4 - 614.4 |

| Output Skew (ps) | 240 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 9 |

| Package Area (mm²) | 100 |

| Pb Free Category | e3 Sn |

| Phase Jitter Typ RMS (ps) | 0.88 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.0 |

| Prog. Clock | No |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 500 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 1 |

| Width (mm) | 10 |

| Xtal Freq (KHz) | 30720 - 30720 |

有关 813076I 的资源

描述

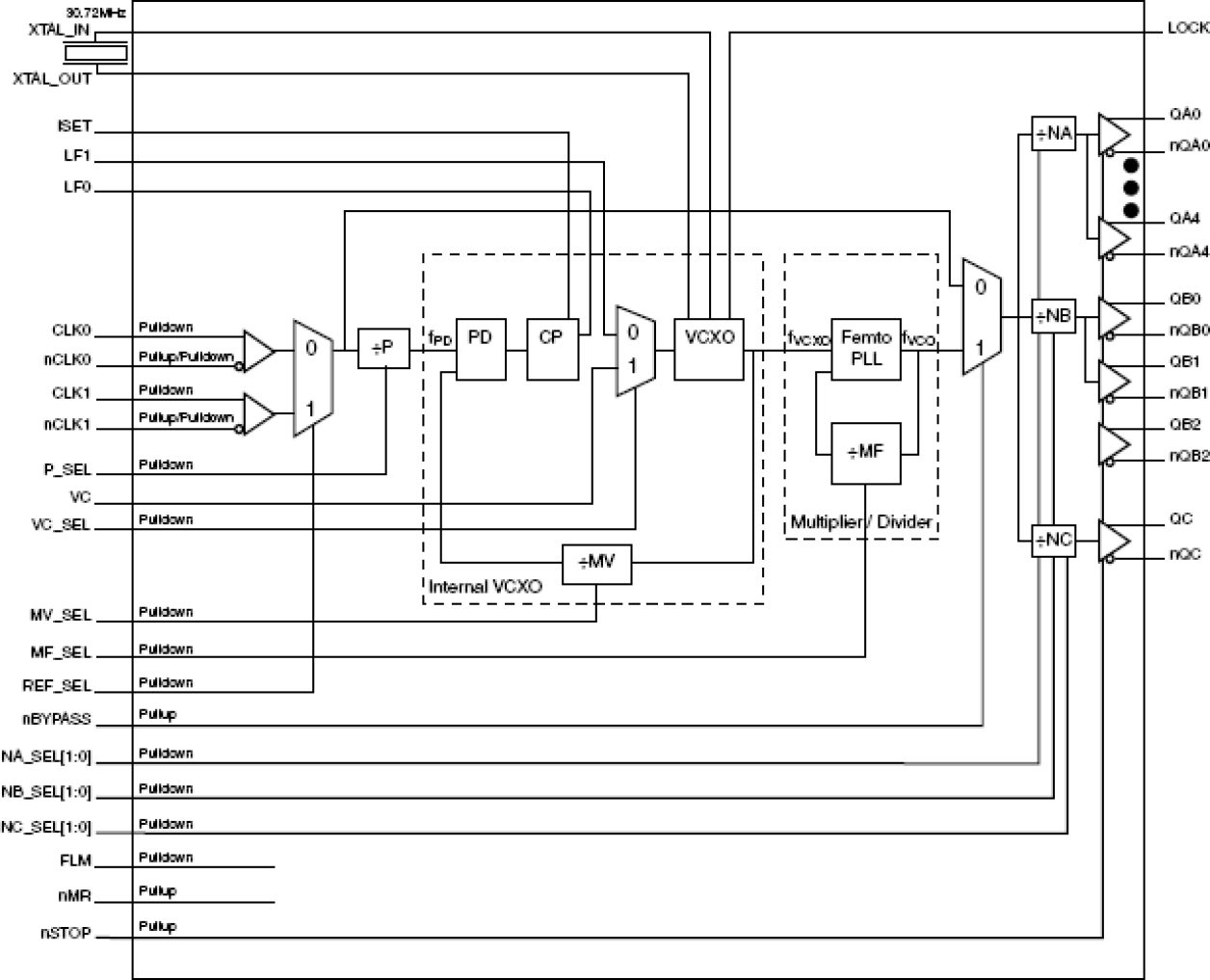

The 813076I is a member of the family of high performance clock solutions from IDT. The 813076I a PLL based synchronous clock solution that is optimized for wireless infrastructure equipment where frequency translation and jitter attenuation is needed.

The device contains two internal PLL stages that are cascaded in series. The first PLL stage attenuates the reference clock jitter by using an internal or external VCXO circuit. The internal VCXO requires the connection of an external inexpensive pullable crystal (XTAL) to the 813076I. This first PLL stage (VCXO PLL) uses external passive loop filter components which are used to optimize the PLL loop bandwidth and damping characteristics for the given application. The output of the first stage VCXO PLL is a stable and jitter-tolerant reference input for the second PLL stage of 30.72MHz. The second PLL stage provides frequency translation by multiplying the output of the first stage up to 614.4MHz. The low phase noise characteristics of the clock signal is maintained by the internal FemtoClock® PLL, which requires no external components or configuration. Two independently configurable frequency dividers translate the 491.52MHz or 614.4MHz internal VCO signal to the desired output frequencies. All frequency translation ratios are set by device configuration pins. Alternative to the clock frequency multiplication functionality, the 813076I can work as a VCXO. Enabling the VCXO mode allows the output frequency of 614.4MHz/N or 491.52MHz/N to be pulled by the input voltage of the VC pin.