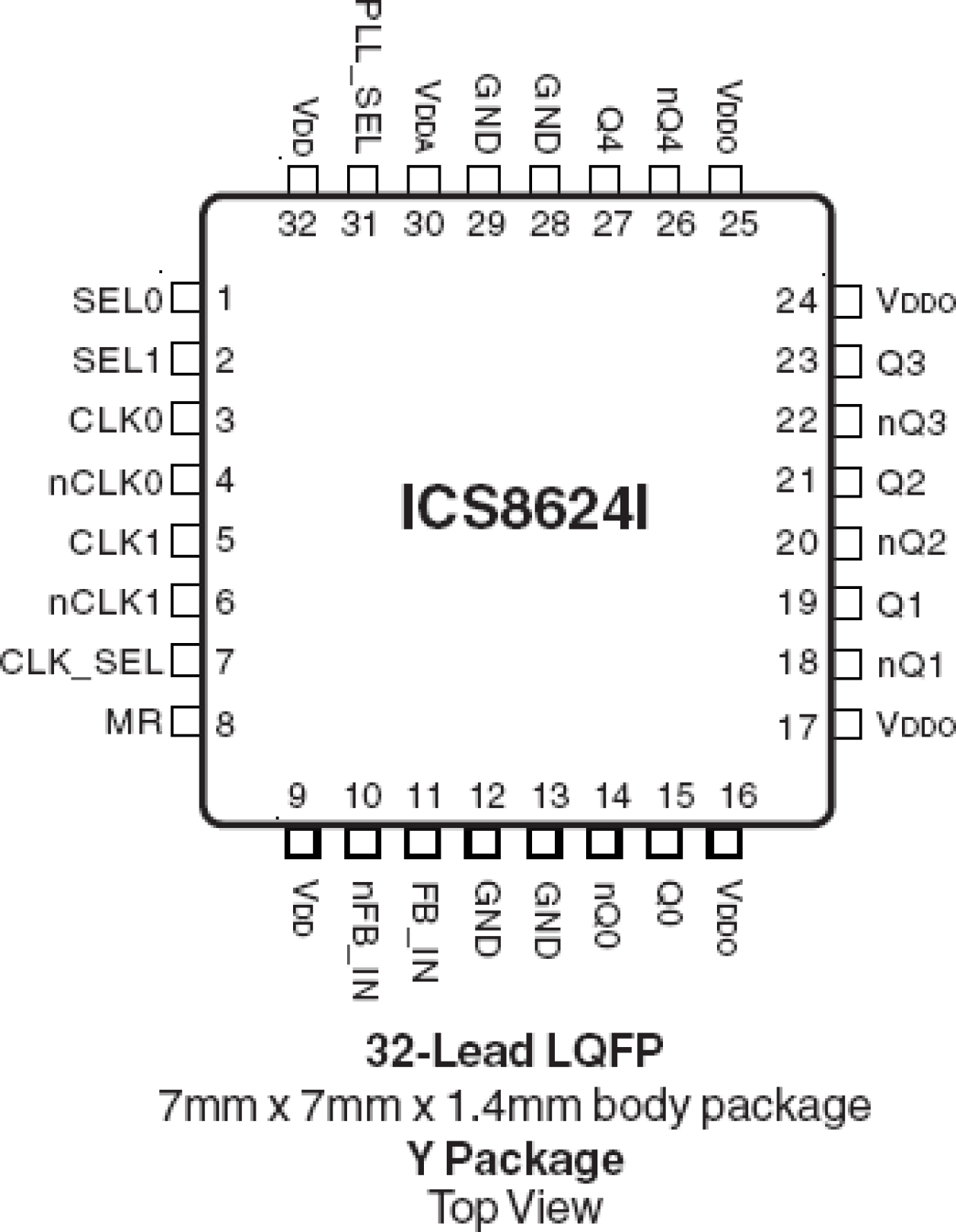

封装信息

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.8 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | TQFP |

| Lead Count (#) | 32 |

| Pb (Lead) Free | Yes |

| Carrier Type | Reel |

| Advanced Features | Feedback Input |

| C-C Jitter Max P-P (ps) | 35 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 31.25 - 630 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 2 |

| Length (mm) | 7 |

| MOQ | 1000 |

| Moisture Sensitivity Level (MSL) | 3 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 31.25 - 630 |

| Output Skew (ps) | 50 |

| Output Type | HSTL |

| Output Voltage (V) | 1.8 |

| Outputs (#) | 5 |

| Package Area (mm²) | 49 |

| Pb Free Category | e3 Sn |

| Phase Jitter Max RMS (ps) | 50 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Prog. Clock | No |

| Qty. per Carrier (#) | 0 |

| Qty. per Reel (#) | 1000 |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

有关 8624I 的资源

描述

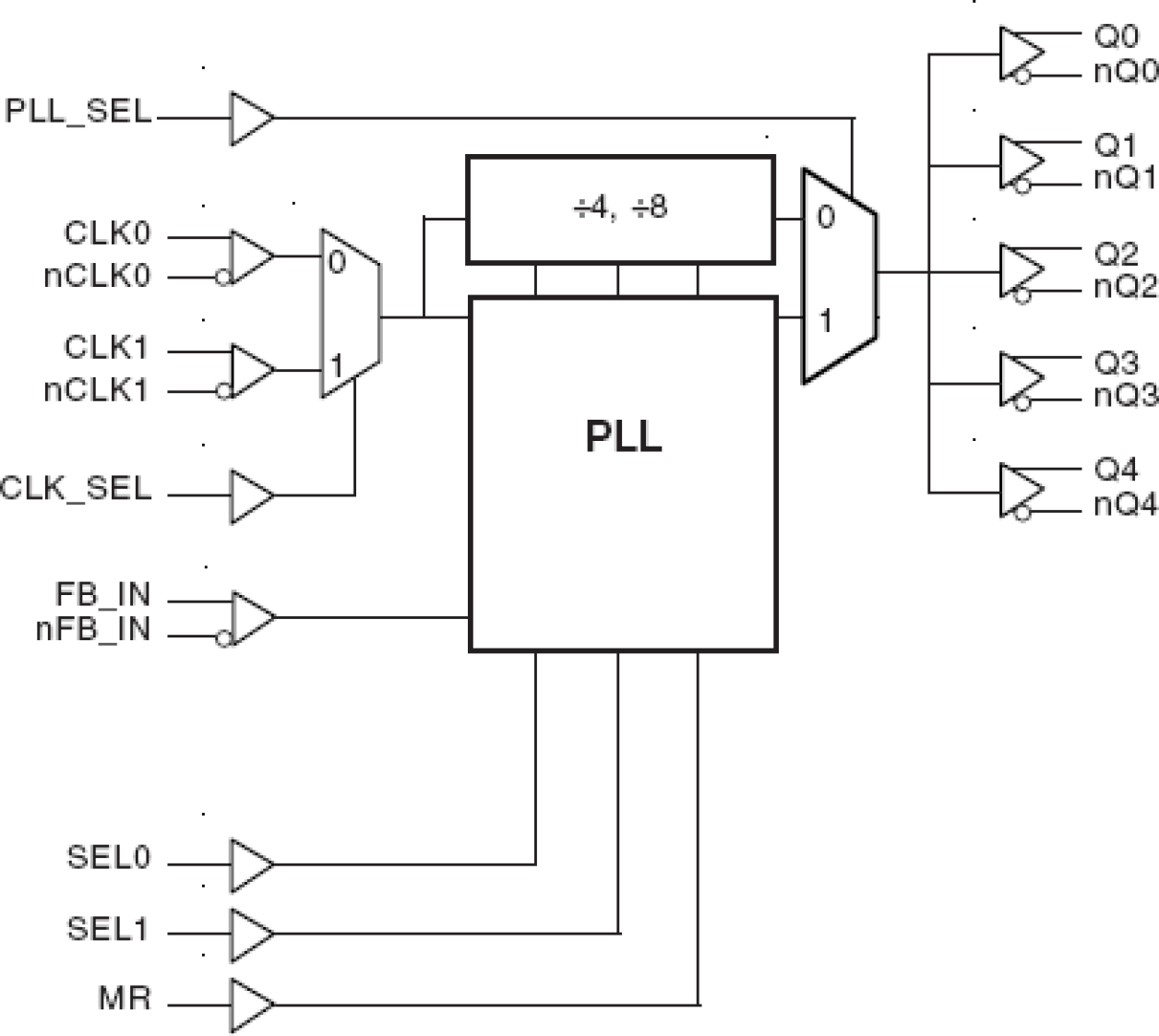

The 8624I is a high performance, 1-to-5 Differential-to-HSTL zero delay buffer. The 8624I has two selectable clock input pairs. The CLK0, nCLK0 and CLK1, nCLK1 pair can accept most standard differential input levels. The VCO operates at a frequency range of 250MHz to 630MHz. Utilizing one of the outputs as feedback to the PLL, output frequencies up to 630MHz can be regenerated with zero delay with respect to the input. Dual reference clock inputs support redundant clock or multiple reference applications..