封装信息

| CAD 模型: | View CAD Model |

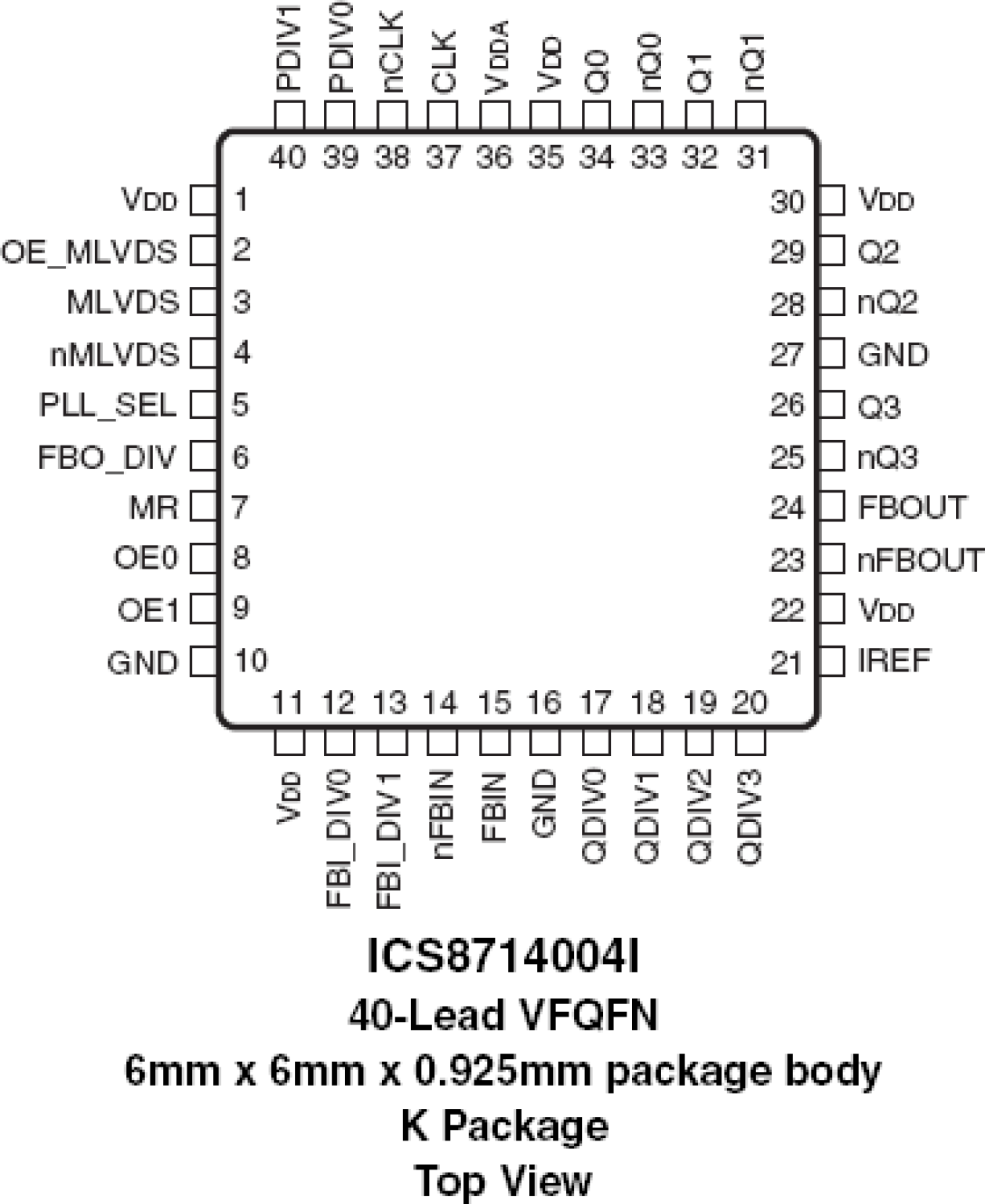

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG40 |

| Lead Count (#): | 40 |

| Pkg. Dimensions (mm): | 6.0 x 6.0 x 0.9 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 40 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 5000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Advanced Features | Feedback Input |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2 |

| C-C Jitter Typ P-P (ps) | 35 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 19.6 - 165 |

| Input Type | LVPECL, LVDS, M-LVDS, LVHSTL, HCSL |

| Inputs (#) | 2 |

| Length (mm) | 6 |

| MOQ | 5000 |

| Output Banks (#) | 4 |

| Output Freq Range (MHz) | 98 - 165 |

| Output Skew (ps) | 60 |

| Output Type | HCSL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 4 |

| Package Area (mm²) | 36 |

| Phase Jitter Typ RMS (ps) | 0.62 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 6.0 x 6.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Product Category | Zero Delay Buffers |

| Prog. Clock | No |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | Yes |

| Thickness (mm) | 0.9 |

| Width (mm) | 6 |

有关 8714004I 的资源

描述

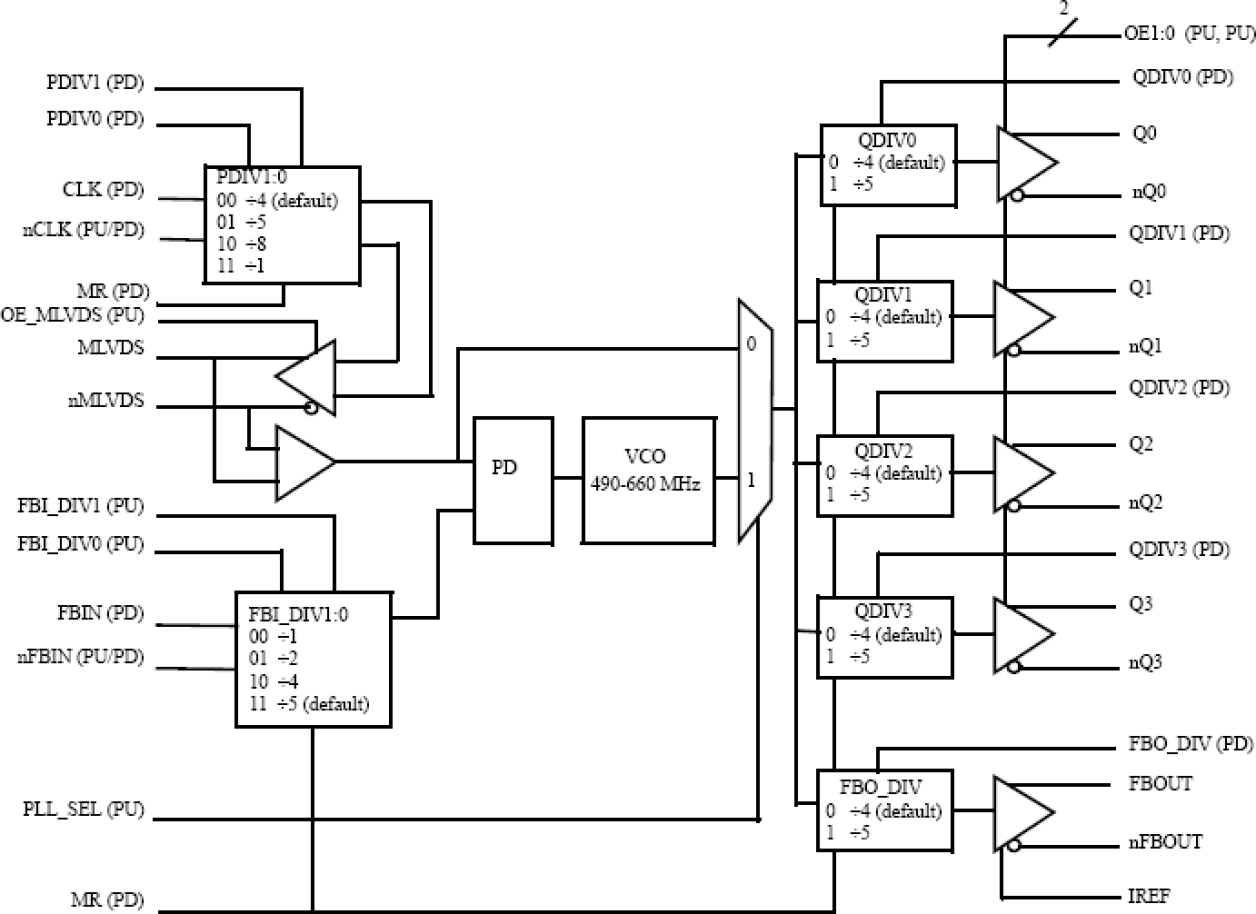

The 8714004I is Zero-Delay Buffer/Frequency Multiplier with eight differential HCSL output pairs, and uses external feedback (differential feedback input and output pairs) for "zero delay" clock regeneration. In PCI Express® and Ethernet applications, 100MHz and 125MHz are the most commonly used reference clock frequencies and each of the eight output pairs can be independently set for either 100MHz or 125MHz. With an output frequency range of 98MHz to 165MHz, the device is also suitable for use in a variety of other applications such as Fibre Channel (106.25MHz) and XAUI (156.25MHz). The M-LVDS Input/Output pair is useful in backplane applications when the reference clock can either be local (on the same board as the 8714004I) or remote via a backplane connector. In output mode, an input from a local reference clock applied to the CLK/nCLK input pins is translated to M-LVDS and driven out to the MLVDS/nMLVDS pins. In input mode, the internal M-LVDS driver is placed in Hi-Z state using the OE_MLVDS pin and MLVDS/nMLVDS pin then becomes an input (e.g. from a backplane). The 8714004I uses very low phase noise FemtoClock technology, thus making it ideal for such applications as PCI Express Generation 1 and 2 as well as for Gigabit Ethernet, Fibre Channel, and 10 Gigabit Ethernet. It is packaged in a 40-VFQFN package (6mm x 6mm).