封装信息

| CAD 模型: | View CAD Model |

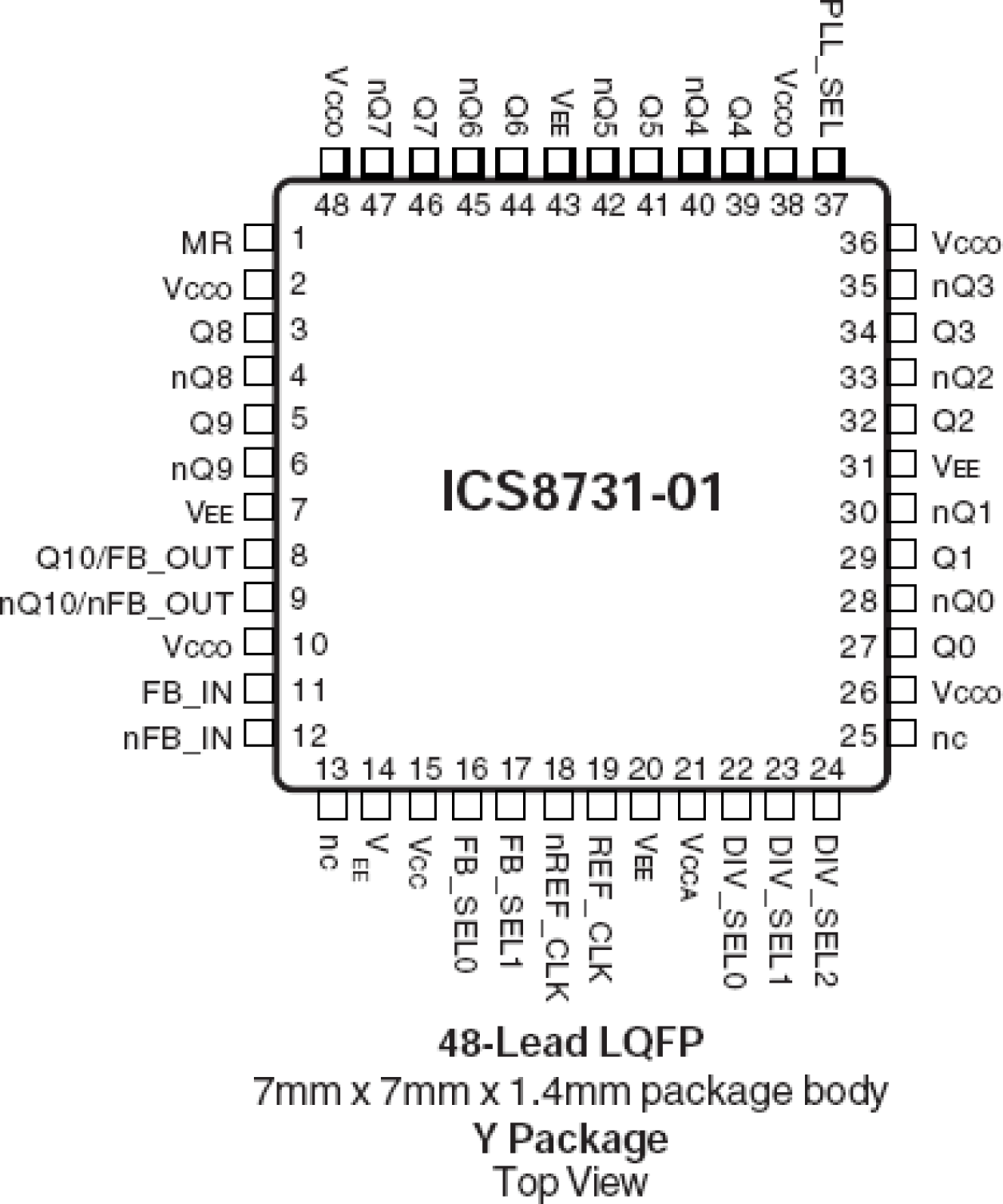

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG48 |

| Lead Count (#): | 48 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 48 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 250 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Advanced Features | Feedback Input |

| C-C Jitter Max P-P (ps) | 65 |

| Core Voltage (V) | 3.3 |

| Feedback Input | Yes |

| Input Freq (MHz) | 200 |

| Input Type | HCSL, HSTL, LVDS, LVPECL, SSTL |

| Inputs (#) | 1 |

| Length (mm) | 7 |

| MOQ | 250 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 700 |

| Output Skew (ps) | 70 |

| Output Type | LVPECL |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 11 |

| Package Area (mm²) | 49 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Pkg. Type | TQFP |

| Product Category | Zero Delay Buffers |

| Prog. Clock | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

有关 8731-01 的资源

描述

The 8731-01 is a low voltage, low skew, 1-to-11 Differential-to-3.3V LVPECL Clock Multiplier/Zero Delay Buffer. With output frequencies up to 700MHz the 8731-01 is targeted at high performance clock applications. Along with a fully integrated PLL the 8731- 01 contains frequency configurable, differential outputs and external feedback inputs for multiplying clock frequencies and regenerating clocks with "zero delay". Frequency multiplication is achieved by utilizing the separate feedback and clock output dividers. The value of the multiplier is determined by the ratio of the feedback divider, M, to the output divider,N. For multiplier values greater than 1, M must be greater than N. For multiplier values less than 1,M must be less than N. The zero delay mode is achieved with M and N at equal values. The divide values of the clock and feedback outputs are controlled by the DIV_SEL0:2 and FB_SEL0:1 inputs, respectively. The 8731-01 accepts any differential signal and translates it to differential 3.3V LVPECL output levels.