特性

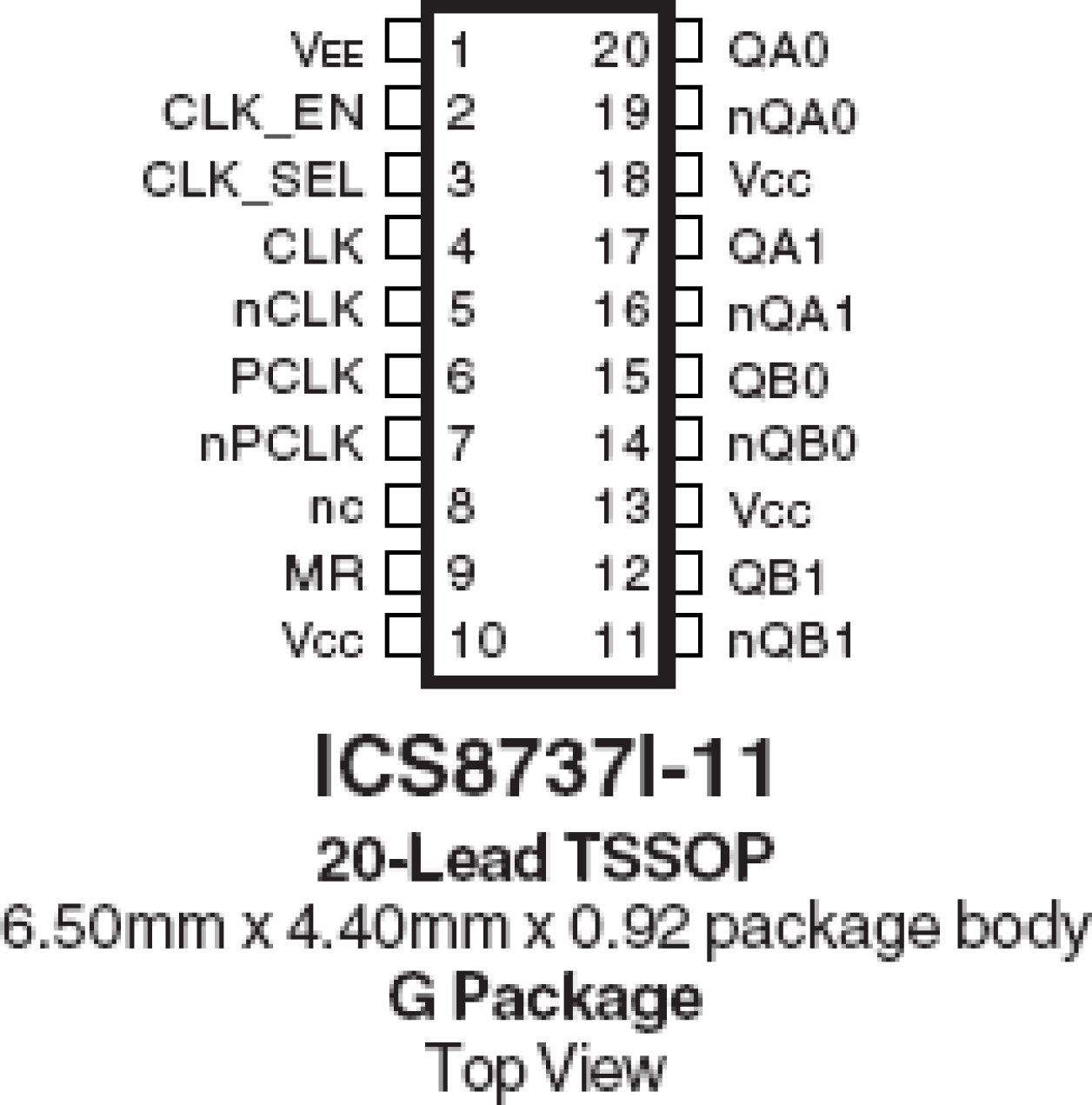

- Two divide by 1 differential 3.3V LVPECL outputs

- Two divide by 2 differential 3.3V LVPECL outputs

- Selectable differential CLK, nCLK or LVPECL clock inputs

- CLK, nCLK pair can accept the following differential input levels: LVDS, LVPECL, LVHSTL, SSTL, HCSL

- PCLK, nPCLK supports the following input types: LVPECL, CML, SSTL

- Maximum output frequency: 650MHz

- Translates any single ended input signal (LVCMOS, LVTTL, GTL) to LVPECL levels with resistor bias on nCLK input

- Output skew: 75ps (maximum)

- Part-to-part skew: 300ps (maximum)

- Bank skew: Bank A - 30ps (maximum) Bank B - 45ps (maximum)

- 3.3V operating supply

- -40°C to 85°C ambient operating temperature

- Available in lead-free RoHS-compliant package

描述

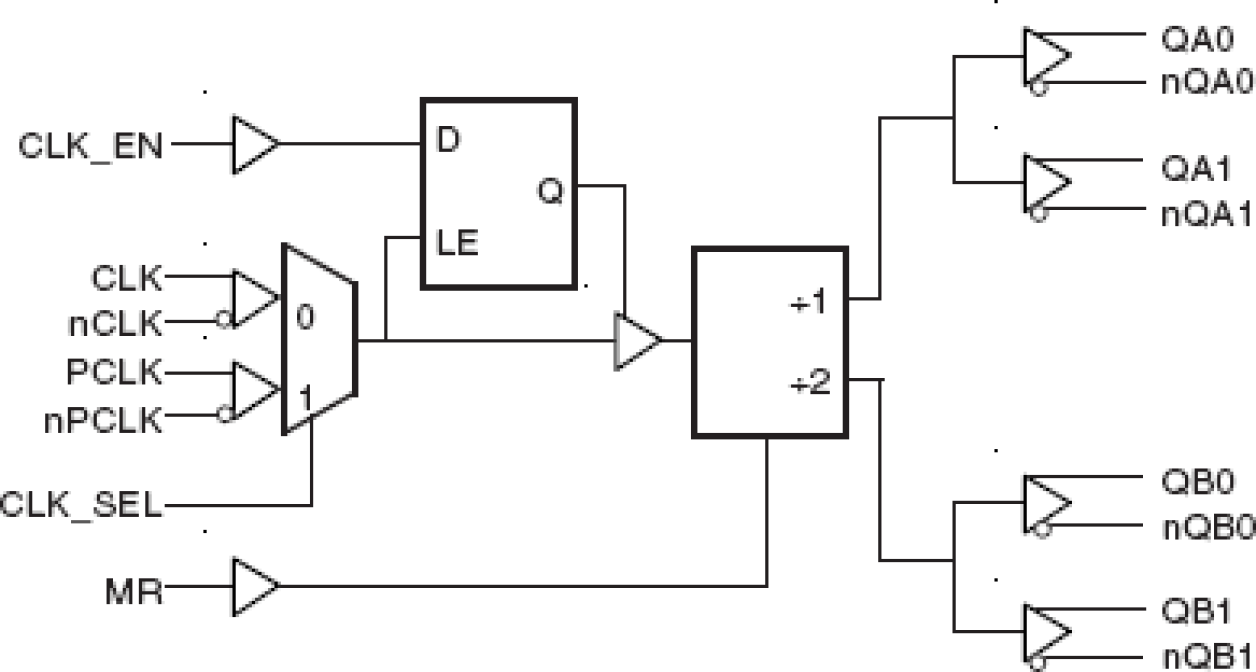

The 8737I-11 is a low skew, high performance Differential-to-3.3V LVPECL Clock Generator/Divider. The 8737I-11 has two selectable clock inputs. The CLK, nCLK pair can accept most standard differential input levels. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin. Guaranteed output and part-to-part skew characteristics make the 8737I-11 ideal for clock distribution applications demanding well defined performance and repeatability.

当前筛选条件