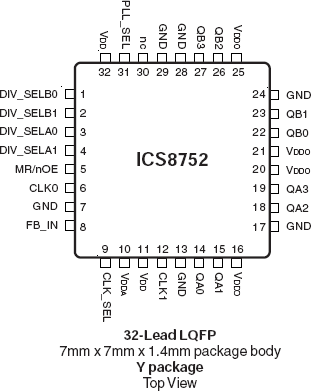

封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.8 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 32 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 250 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Advanced Features | Feedback Input |

| C-C Jitter Max P-P (ps) | 75 |

| Core Voltage (V) | 2.5V, 3.3V |

| Feedback Input | Yes |

| Input Freq (MHz) | 18.33 - 240 |

| Input Type | LVCMOS |

| Inputs (#) | 2 |

| Length (mm) | 7 |

| MOQ | 250 |

| Output Banks (#) | 2 |

| Output Freq Range (MHz) | 18.33 - 240 |

| Output Skew (ps) | 90 |

| Output Type | LVCMOS |

| Output Voltage (V) | 2.5V, 3.3V |

| Outputs (#) | 8 |

| Package Area (mm²) | 49 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Pkg. Type | TQFP |

| Prog. Clock | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

| 已发布 | No |

有关 8752 的资源

描述

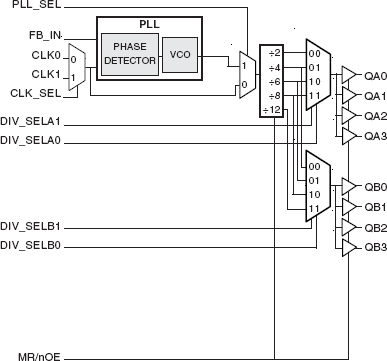

The 8752 is a low voltage, low skew LVCMOS clock generator. With output frequencies up to 240MHz, the 8752 is targeted for high performance clock applications. Along with a fully integrated PLL, the 8752 contains frequency configurable outputs and an external feedback input for regenerating clocks with "zero delay".

Dual clock inputs, CLK0 and CLK1, support redundant clock applications. The CLK_SEL input determines which reference clock is used. The output divider values of Bank A and B are controlled by the DIV_SELA0:1, and DIV_SELB0:1, respectively.

For test and system debug purposes, the PLL_SEL input allows the PLL to be bypassed. When HIGH, the MR/nOE input resets the internal dividers and forces the outputs to the high impedance state.

The low impedance LVCMOS outputs of the 8752 are designed to drive terminated transmission lines. The effective fanout of each output can be doubled by utilizing the ability of each output to drive two series terminated transmission lines.