封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | CABGA |

| Pkg. Code: | AJG144 |

| Lead Count (#): | 144 |

| Pkg. Dimensions (mm): | 10.0 x 10.0 x 1.2 |

| Pitch (mm): | 0.8 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 144 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 168 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e1 SnAgCu |

| Temp. Range (°C) | -40 to 85°C |

| Country of Assembly | PHILIPPINES |

| Country of Wafer Fabrication | SINGAPORE |

| Application | PTP Timing Card, SETS, Low-cTE Timing Card |

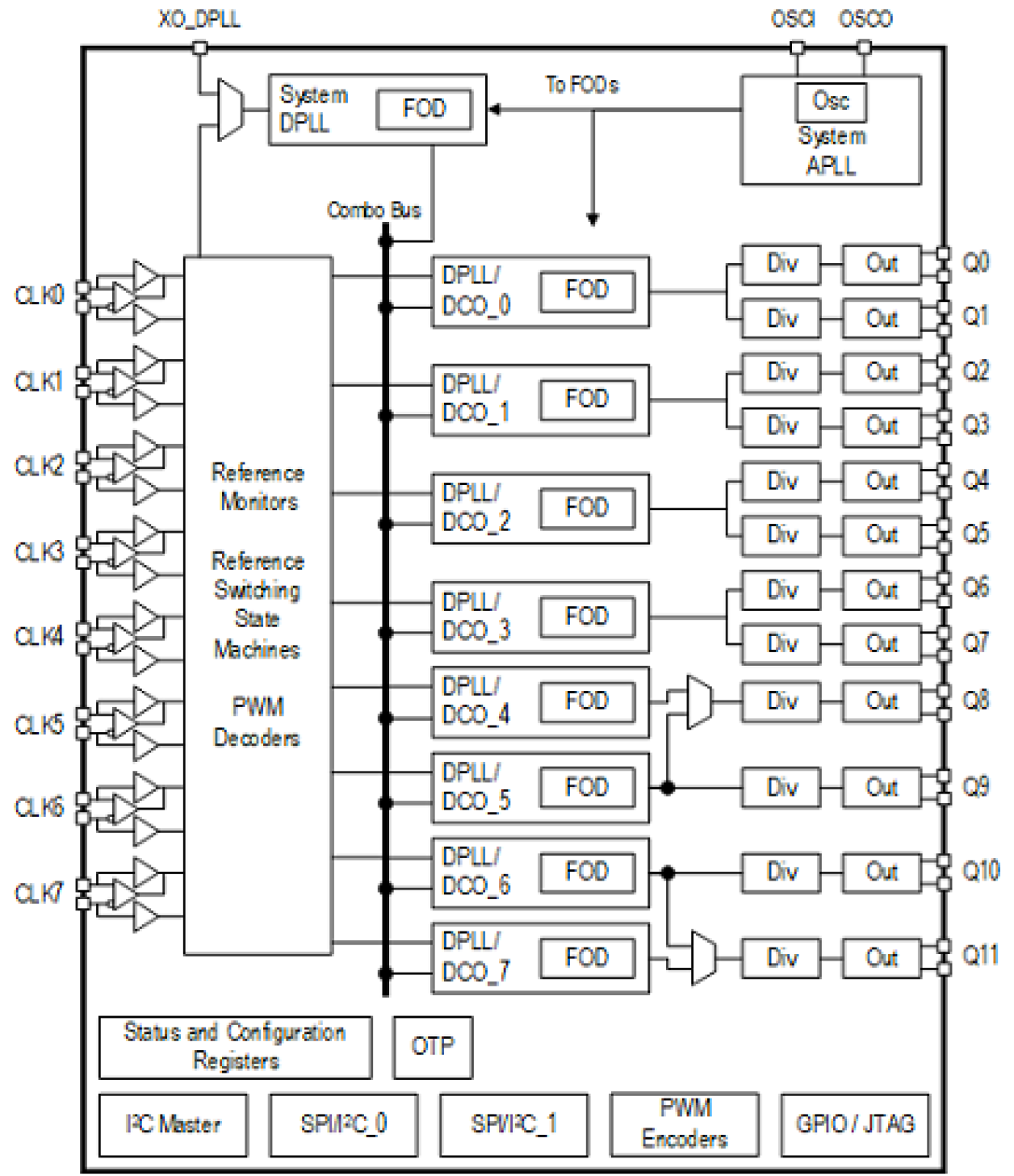

| Channels (#) | 8 |

| Clock Support | G.813, G.8262, G.8262.1, GR-1244-CORE, GR-253-CORE, G.8273.2 |

| Core Voltage (V) | 2.5V, 3.3V |

| Diff. Inputs | 8 |

| Diff. Outputs | 12 |

| Family Name | ClockMatrix |

| Fractional Output Dividers (#) | 8 |

| Function | System Synchronizer |

| Input Freq (MHz) | 5.0E-7 - 1000 |

| Input Type | HCSL, LVDS, LVHSTL, LVPECL, SSTL |

| Inputs (#) | 16 |

| Length (mm) | 10 |

| Longevity | 2040 四月 |

| MOQ | 168 |

| Output Banks (#) | 8 |

| Output Freq Range (MHz) | 5.0E-7 - 1000 |

| Output Skew (ps) | 50 |

| Output Type | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL |

| Output Voltage (V) | 1.2V, 1.5V, 1.8V, 2.5V, 3.3V |

| Outputs (#) | 24 |

| Phase Jitter Max RMS (ps) | 0.2 |

| Phase Jitter Typ RMS (ps) | 0.15 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 10.0 x 10.0 x 1.2 |

| Pkg. Type | CABGA |

| Price (USD) | $57.27363 |

| Product Category | IEEE 1588, ClockMatrix, Ultra-Low Jitter Clocks (<300 fs RMS), Jitter Attenuators, Network Synchronization, Programmable Clocks |

| Prog. Interface | I2C, SPI |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Thickness (mm) | 1.2 |

| Width (mm) | 10 |

| Xtal Freq (KHz) | 25 - 54 |

有关 8A34001 的资源

描述

The 8A34001 system synchronizer for IEEE 1588 generates ultra-low jitter, precision timing signals based on the IEEE 1588 Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE). The device can be used as a single timing and synchronization source for a system or two of these devices can be used as a redundant pair for improved system reliability. Digitally Controlled Oscillators (DCOs) are available to be controlled by IEEE 1588 clock recovery servo software running on an external processor. The device supports physical layer timing with Digital PLLs (DPLLs) and other timing blocks necessary to implement a Synchronous Equipment Timing Source (SETS) for SyncE. The DCOs can be controlled using IEEE 1588 information alone, or they can combine IEEE 1588 time information with physical layer frequency information from SyncE in accordance with ITU-T G.8273.2. The 8A34001 can be used to actively measure and compensate for clock propagation delays across backplanes and across circuit boards to ensure the distribution of accurate time and phase with minimal time error between IEEE 1588 Time Stamp Units (TSUs) in a system. The device supports multiple independent channels that control IEEE 1588 clock synthesis, SyncE clock generation, jitter attenuation, and universal frequency translation. Input-to-input, input-to-output and output-to-output phase skew can all be precisely managed. The device outputs ultra-low jitter clocks that can directly synchronize SerDes running at up to 28Gbps; as well as CPRI/OBSAI, SONET/SDH and PDH interfaces and IEEE 1588 TSUs.

To easily implement synchronization in IEEE 1588 systems, Renesas offers PTP Clock Manager Software for free under license.