封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | VFQFPN |

| Pkg. Code: | NLG100 |

| Lead Count (#): | 100 |

| Pkg. Dimensions (mm): | 12.0 x 12.0 x 0.9 |

| Pitch (mm): | 0.4 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 100 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 168 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| 105°C Max. Case Temp. | 0 |

| Accepts Spread Spec Input | Yes |

| Additive Phase Jitter Typ RMS (fs) | 320 |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3 |

| Architecture | Common |

| Core Voltage (V) | 3.3 |

| Diff. Input Signaling | M-LVDS, LVDS |

| Diff. Inputs | 16 |

| Diff. Output Signaling | M-LVDS |

| Diff. Outputs | 16 |

| Divider Value | 1 |

| Function | Multiplexer |

| Input Freq (MHz) | 350 |

| Input Type | M-LVDS, LVDS |

| Inputs (#) | 16 |

| Length (mm) | 12 |

| MOQ | 168 |

| Output Banks (#) | 16 |

| Output Freq Range (MHz) | 350 |

| Output Type | M-LVDS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 16 |

| PLL | No |

| Package Area (mm²) | 144 |

| Pitch (mm) | 0.4 |

| Pkg. Dimensions (mm) | 12.0 x 12.0 x 0.9 |

| Pkg. Type | VFQFPN |

| Product Category | Clock Buffers & Drivers, Clock Multiplexers, PCI Express Clocks |

| Prog. Clock | No |

| Requires Terms and Conditions | Requires acceptance of Terms and Conditions |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | No |

| Thickness (mm) | 0.9 |

| Width (mm) | 12 |

有关 8V54816 的资源

描述

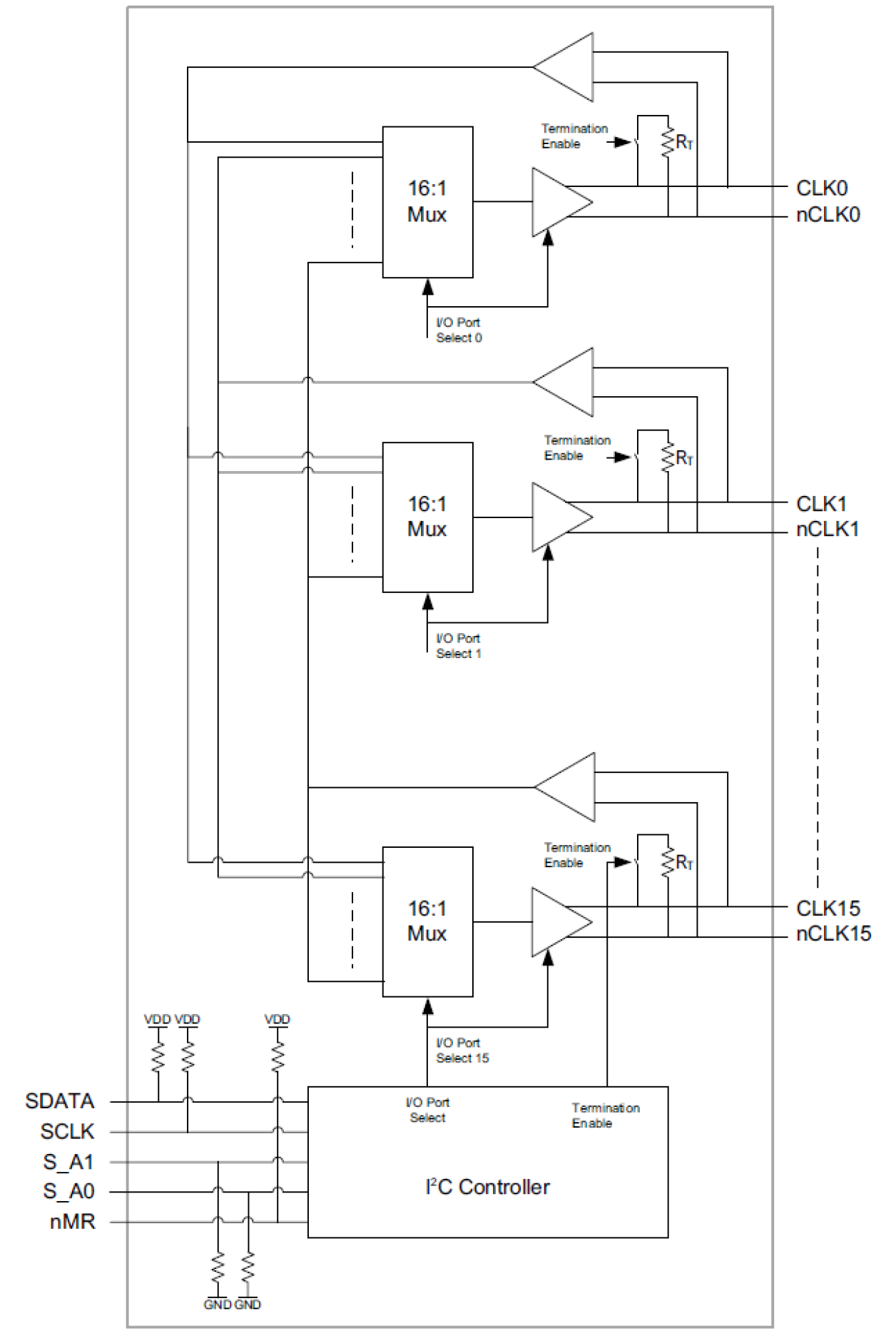

The 8V54816A is a 16-port, bidirectional cross-point clock switch designed for clock distribution in MicroTCA.4 systems. It features 16 bidirectional M-LVDS ports. Each port can be individually set as input or output. Each output port can be connected to any port defined as input. Each port features switchable termination (ON: 100Ω, OFF: High impedance). Output ports can drive up to 19-inch PCB tracks with M-LVDS levels. The device is optimized for very low additive phase noise. Configuration of the device is achieved by I²C. At startup, a default configuration is set where all ports are in High-Impedance mode with outputs disabled.