特性

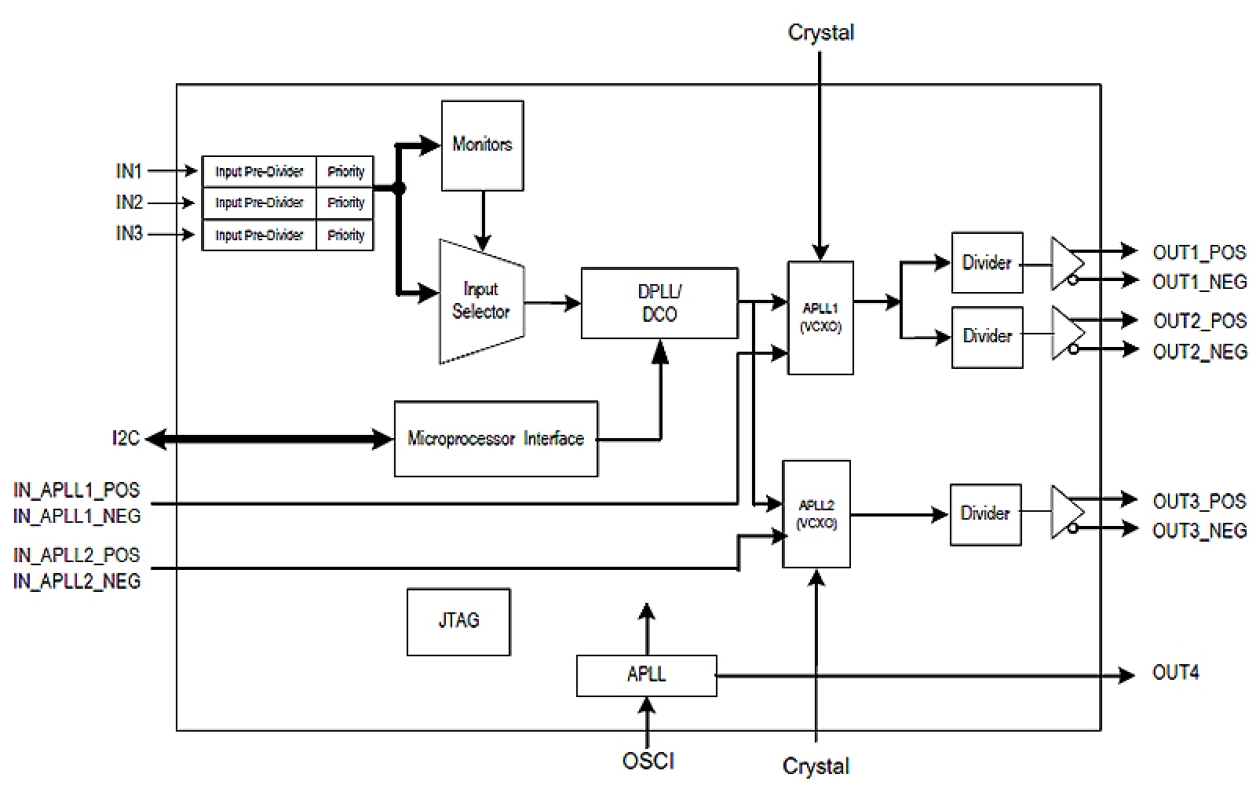

- Digital PLL synchronizes with GPS or Ethernet connected synchronization sources

- DPLL bandwidth is selectable to be 15 mHz or 1.2 Hz

- DPLL holdover accuracy is 1.1X10-5 ppm

- Input references are monitored for frequency offset and activity; DPLL holdover, free run and hitless reference switching can be forced by the host processor or can be automatically controlled by an internal state machine

- Internal DCO has resolution of 0.01105 ppb and can be controlled by an external processor via I2C interface for IEEE 1588 clock generation

- Two Analog PLLs for jitter attenuation and frequency translation

- Jitter generation <0.3ps RMS (10 kHz to 20 MHz), meets jitter requirements of leading PHYs supporting 10GBASE-R, QSGMII and XAUI

- IN1, IN2 and IN3 accept single ended reference clocks whose frequencies can be 1PPS (1 Hz), 25 MHz, 125 MHz or 156.25 MHz

- OUT1 and OUT2 output differential clocks with frequencies of 125 MHz or 156.25 MHz

- OUT3 outputs a differential clock with frequency of 322.265625 MHz or 644.53125 MHz

- OUT4 outputs a free-running LVCMOS clock with frequency of 25 MHz

描述

The IDT8V89317 is used to frequency synchronize equipment with an Ethernet connected reference or with a GPS based 1PPS reference; its integrated DCO (Digitally Controlled Oscillator) can be controlled by an external IEEE 1588 clock recovery servo to synthesize IEEE 1588-based clocks. The IDT8V89317 ultra-low jitter output clocks can be used to directly time 10 Gigabit Ethernet PHYs and QSGMII devices.

当前筛选条件