特性

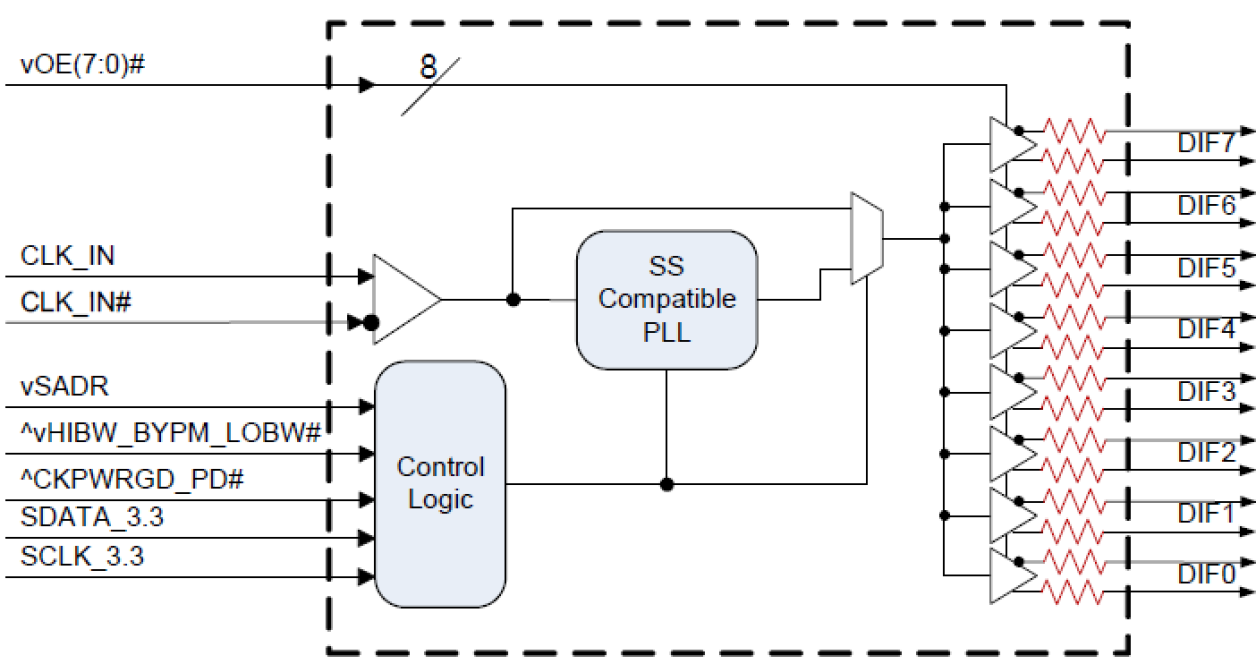

- LP-HCSL outputs save 32 resistors; minimal board space and BOM cost

- 62mW typical power consumption in PLL mode; eliminates thermal concerns

- Spread Spectrum (SS) compatible; allows use of SS for EMI reduction

- OE# pins: support DIF power management

- HCSL compatible differential input: can be driven by common clock sources

- Programmable slew rate for each output: allows tuning for various line lengths

- Programmable output amplitude: allows tuning for various application environments

- Pin/Software selectable PLL bandwidth and PLL bypass: minimize phase jitter for each application

- Outputs blocked until PLL is locked: clean system start-up

- Software selectable 50MHz or 125MHz PLL operation: useful for Ethernet applications

- Configuration can be accomplished with strapping pins: SMBus interface not required for device control

- 3.3V tolerant SMBus interface works with legacy controllers

- Space-saving 6mm x 6mm 48-VFQFPN: minimal board space

- Selectable SMBus addresses; multiple devices can easily share an SMBus segment

描述

The 9DBV0841 1.8V PCIe Gen 1-3 zero-delay/fanout clock buffer has integrated output terminations providing Zo = 100Ω for direct connection for 100Ω transmission lines. The device has eight output enables for clock management and three selectable SMBus addresses.

应用

- SSD

- microServers

- WLAN access points