封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TSSOP |

| Pkg. Code: | PAG56 |

| Lead Count (#): | 56 |

| Pkg. Dimensions (mm): | 14.0 x 6.1 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 56 |

| Carrier Type | Reel |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 2000 |

| Qty. per Carrier (#) | 0 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | 0 to 70°C |

| Accepts Spread Spec Input | Yes |

| Advanced Features | HiBW frequency translation capability |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, FBD |

| Chipset Manufacturer | Intel |

| Clock Spec. | DB1200GS |

| Diff. Input Signaling | HCSL |

| Diff. Inputs | 1 |

| Diff. Output Signaling | HCSL |

| Diff. Outputs | 12 |

| Diff. Termination Resistors | 48 |

| Function | Buffer |

| Length (mm) | 14 |

| MOQ | 2000 |

| Output Enable (OE) Pins | 11 |

| Output Freq Range (MHz) | 400 |

| Package Area (mm²) | 85.4 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 14.0 x 6.1 x 1.0 |

| Pkg. Type | TSSOP |

| Power Consumption Typ (mW) | 970 |

| Product Category | Processor Clock Buffers |

| Reel Size (in) | 13 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Supply Voltage (V) | 3.3 - 3.3 |

| Tape & Reel | Yes |

| Thickness (mm) | 1 |

| Width (mm) | 6.1 |

有关 9FG1200-1 的资源

描述

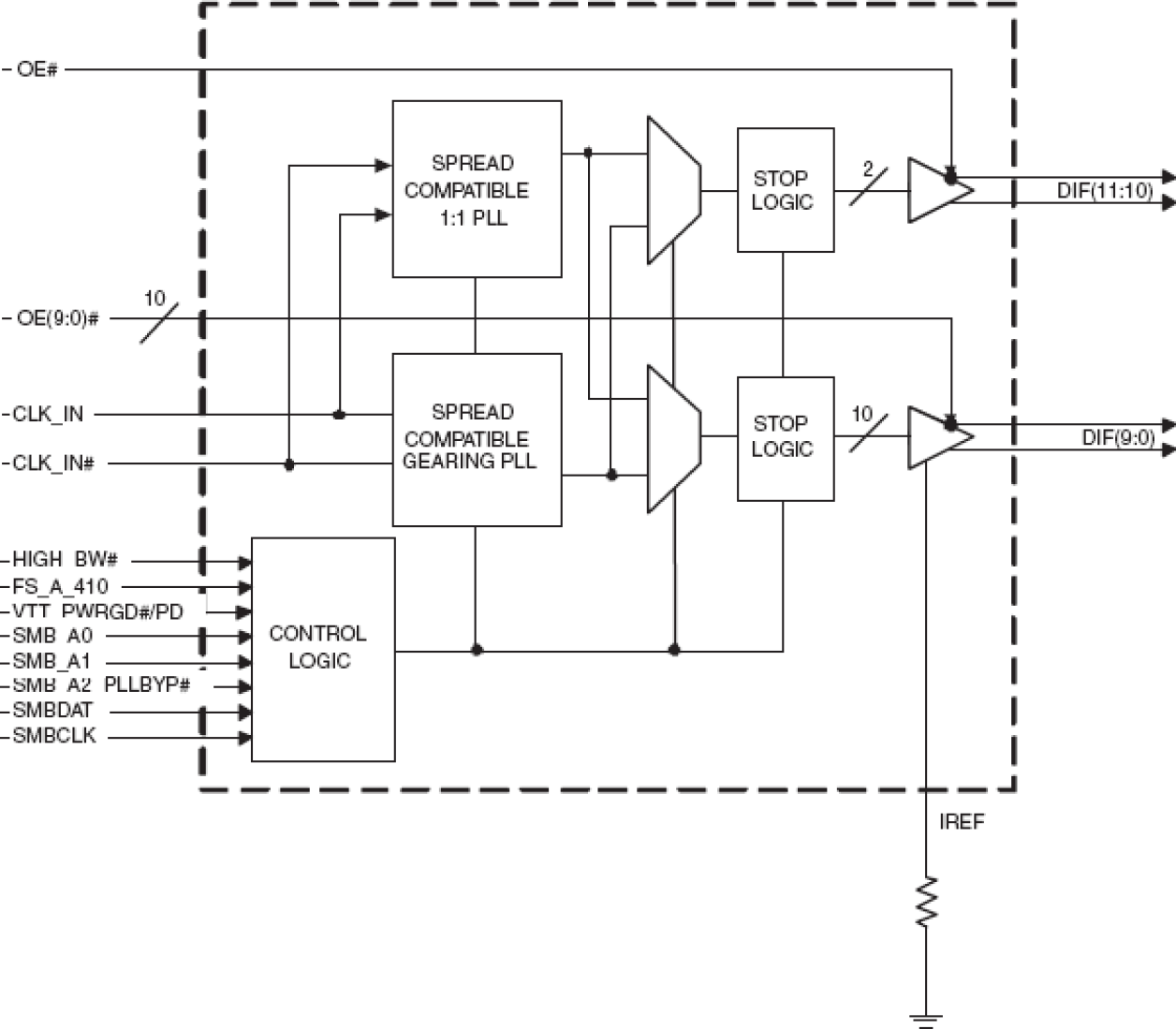

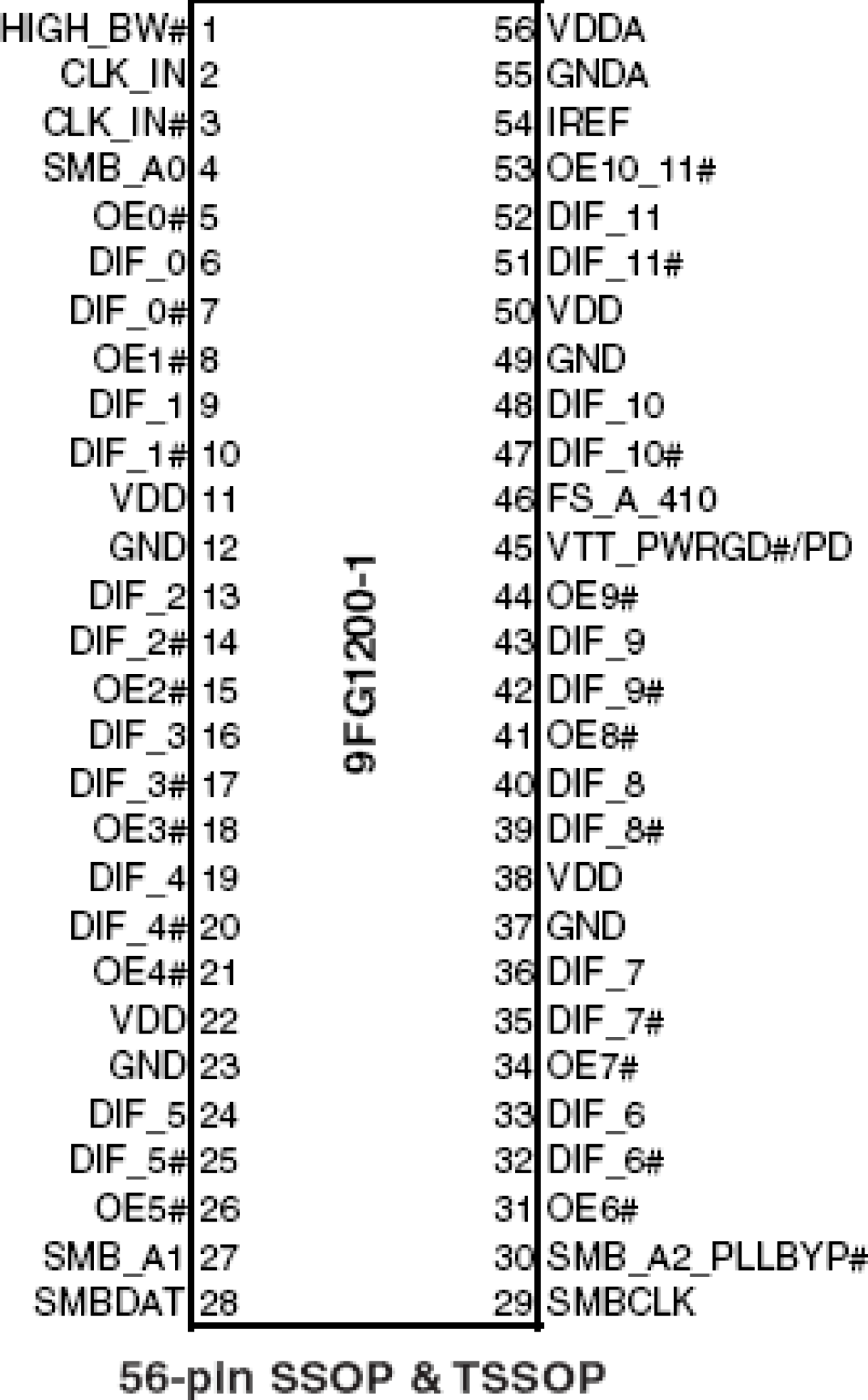

9FG1200-1 follows the Intel DB1200GS Differential Buffer Specification. This buffer provides 12 output clocks for CPU Host Bus, PCIe Gen2, or Fully Buffered DIMM applications. The outputs are configured with two groups. Both groups (DIF 9:0) and (DIF 11:10) can be equal to or have a gear ratio to the input clock. A differential CPU clock from a CK410B+ main clock generator, such as the 932S421, drives the . The can provide outputs up to 400MHz.