特性

- Single 1.7V - 2.0V supply

- 64Mbit (8 x 8Mbit) Flash memory

- Serial Peripheral Interface (SPI) and Quad Peripheral Interface (QPI) compatible

- Supports SPI modes 0 and 3

- Supports dual-output read and quad I/O program and read

- Supports QPI program and read

- 133MHz maximum operating frequency

- Clock-to-Output (tV1) of 6ns

- Up to 66MB/s continuous data transfer rate

- Quad enabled

- Full chip erase

- Flexible, optimized erase architecture for code and data storage applications

- 0.6ms typical Page Program (256 Bytes) time

- 60ms typical 4kByte Block Erase time

- 200ms typical 32kByte Block Erase time

- 350ms typical 64kByte Block Erase time

- Hardware-controlled locking of Status registers via WP pin

- 4kbit secured One-Time Programmable (OTP) security register

- Hardware write protection

- Serial Flash Discoverable Parameters (SFDP) register

- Flexible programming

- Byte/Page program (1 to 256 Bytes)

- Dual or quad input byte/page program (1 to 256 Bytes)

- Erase/Program suspend and resume

- JEDEC standard manufacturer and device ID read methodology

- Low power dissipation

- 2μA Deep Power-Down (DPD) current (typical)

- 10μA Standby current (typical)

- 5mA Active read current (typical)

- Endurance: 100,000 program/erase cycles (4kB, 32kB, or 64kB blocks)

- Data Retention: 20 years

- Industrial temperature range: -40°C to +85°C

- Industry standard green (Pb/Halide-free/RoHS-compliant) package options

- 8-pad DFN (6mm x 5mm x 0.6mm)

- 8-lead 208-mil SOIC

- 8-ball WLCSP

描述

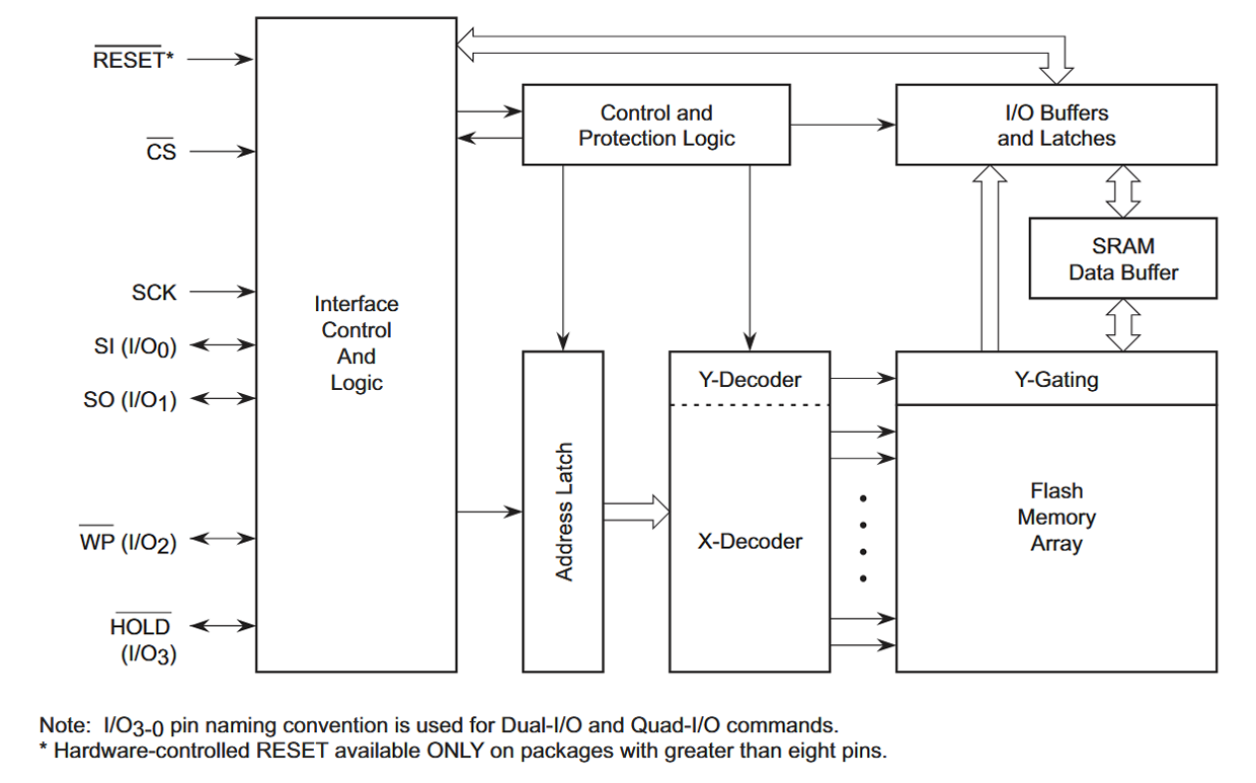

The AT25QL641 is a member of our standard class code and data storage solutions designed for low-voltage systems in which program code is shadowed from Flash memory into embedded or external RAM for execution.

The architecture includes standard erase block sizes and a security register for unique device serialization, system-level Electronic Serial Number (ESN) storage, locked key storage, etc.

The AT25QL641 is Quad enabled at the factory and offers a universally compatible pinout and command set, standard block architecture, and continuous read, wrap, and burst modes for XiP.

当前筛选条件