封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | SBDIP |

| Pkg. Code: | DAV |

| Lead Count (#): | 16 |

| Pkg. Dimensions (mm): | 20.3 x 7.5 x 2.41 |

| Pitch (mm): | 2.5 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pb (Lead) Free | Exempt |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Pkg. Type | SBDIP |

| Lead Count (#) | 16 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pitch (mm) | 2.5 |

| Pkg. Dimensions (mm) | 20.3 x 7.5 x 2.41 |

| DLA SMD | 5962R9660802VEC |

| Pb (Lead) Free | Exempt |

| Pb Free Category | Gold Plate over compliant Undercoat-e4 |

| MOQ | 25 |

| Temp. Range (°C) | -55 to +125°C |

| DSEE (MeV·cm2/mg) | 75 |

| Length (mm) | 20.3 |

| Qualification Level | QML Class V (space) |

| Rating | Space |

| TID HDR (krad(Si)) | 100 |

| TID LDR (krad(Si)) | ELDRS free |

| Thickness (mm) | 2.41 |

| Width (mm) | 7.5 |

有关 CD40193BMS 的资源

描述

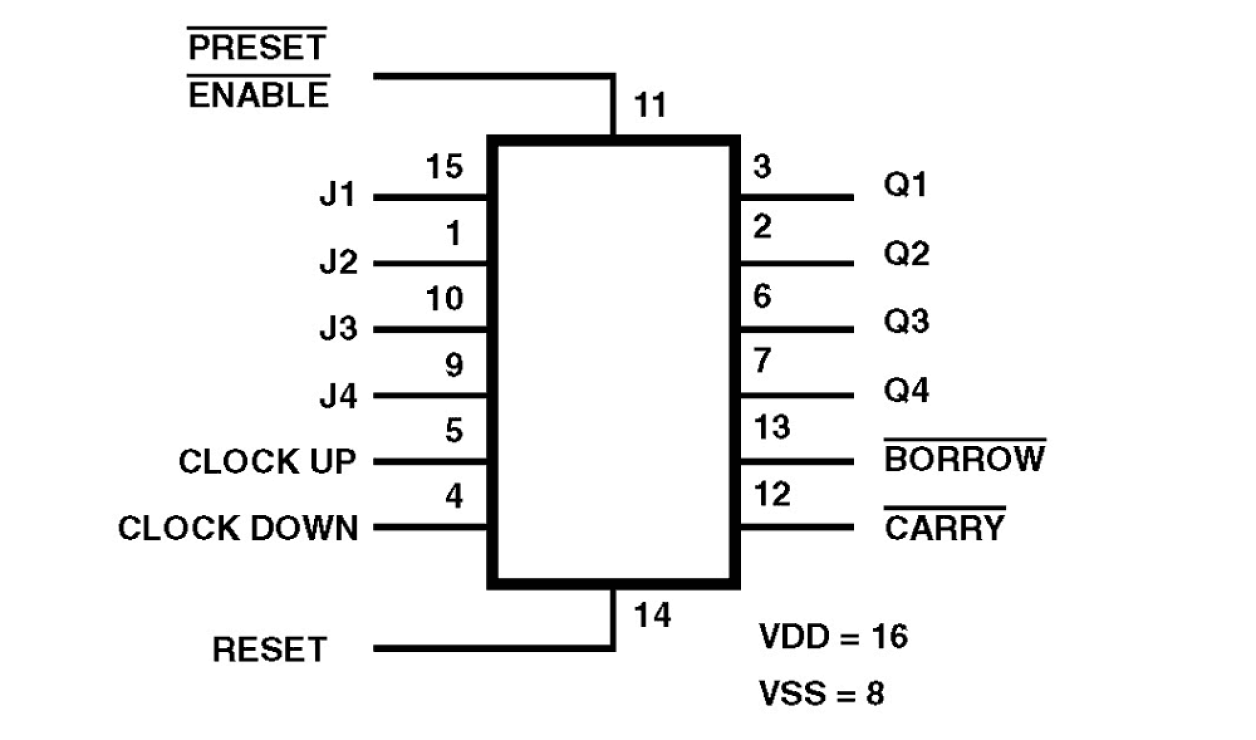

CD40192BMS presettable BCD up/down counter and the CD40193BMS presettable binary up/down counter each consist of four synchronously clocked, gated D type flip-flops connected as a counter. The inputs consist of four individual jam lines, a PRESET ENABLE control, individual CLOCK UP and CLOCK DOWN signals, and a master RESET. Four buffered Q signal outputs as well as CARRY and BORROW outputs for multiple-stage counting schemes are provided. The counter is cleared so that all outputs are in a low state by a high on the RESET line. A RESET is accomplished asynchronously with the clock. Each output is individually programmable asynchronously with the clock to the level on the corresponding jam input when the PRESET ENABLE control is low. The counter counts up one count on the positive clock edge of the CLOCK UP signal provided the CLOCK DOWN line is high. The counter counts down one count on the positive clock edge of the CLOCK DOWN signal provided the CLOCK UP line is high. The CARRY and BORROW signals are high when the counter is counting up or down. The CARRY signal goes low one-half clock cycle after the counter reaches its maximum count in the count-up mode. The BORROW signal goes low one-half clock cycle after the counter reaches its minimum count in the countdown mode. Cascading of multiple packages is easily accomplished without the need for additional external circuitry by tying the BORROW and CARRY outputs to the CLOCK DOWN and CLOCK UP inputs, respectively, of the succeeding counter package. The CD40192BMS and CD40193BMS are supplied in these 16-lead outline packages: Braze Seal DIP H4W (CD40192BMS) and H4X (CD40193BMS), Frit Seal DIP H1F, and Ceramic Flatpack H6P (CD40192BMS) and H6W (CD40193BMS).