封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | CFP |

| Pkg. Code: | KBG |

| Lead Count (#): | 16 |

| Pkg. Dimensions (mm): | 10.4 x 6.9 x 0.00 |

| Pitch (mm): | 1.3 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pb (Lead) Free | Exempt |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | CFP |

| Lead Count (#) | 16 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | Not Applicable |

| DLA SMD | 5962R9675701VXC |

| Pb (Lead) Free | Exempt |

| Pb Free Category | Gold Plate over compliant Undercoat-e4 |

| MOQ | 25 |

| Temp. Range (°C) | -55 to +125°C |

| CAGE code | 34371 |

| Comparator Type | 4-Bit |

| Length (mm) | 10.4 |

| Pitch (mm) | 1.3 |

| Pkg. Dimensions (mm) | 10.4 x 6.9 x 0.00 |

| Qualification Level | QML Class V (Space) |

| Rating | Space |

| SMD URL | 96674 |

| Supply Voltage (max) (V) | 3 - 18 |

| TID HDR (krad(Si)) | 100 |

| Width (mm) | 6.9 |

有关 CD4063BMS 的资源

描述

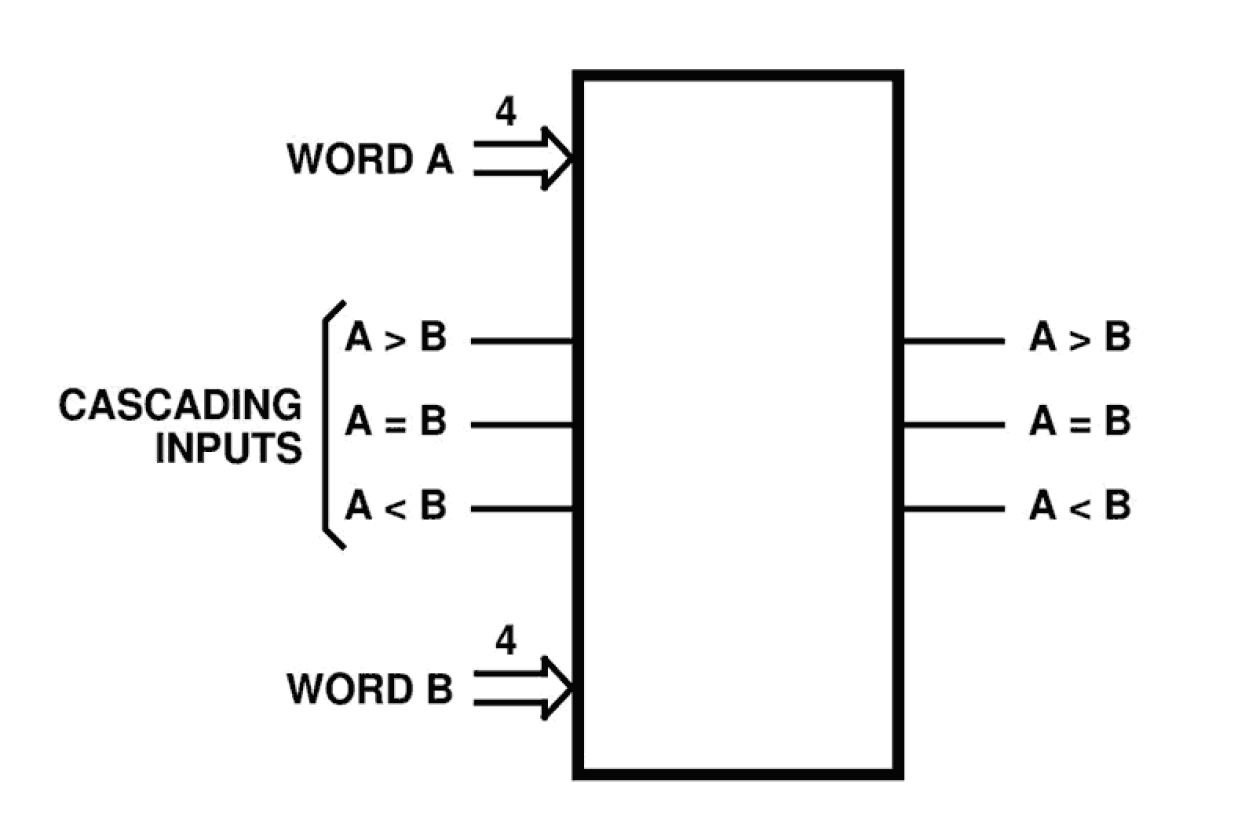

CD4063BMS is a 4-bit magnitude comparator designed for use in computer and logic applications that require the comparison of two 4-bit words. This logic circuit determines whether one 4-bit word (Binary or BCD) is less than, equal to, or greater than a second 4-bit word. The CD4063BMS has eight comparing inputs (A3, B3, through A0, B0), three outputs (A < B, A = B, A > B) and three cascading inputs (A < B, A = B, A > B) that permit systems designers to expand the comparator function to 8, 12, 16. . . 4N bits. When a single CD4063BMS is used, the cascading inputs are connected as follows: (A < B) = low, (A = B) = high, (A > B) = low. For words longer than 4 bits, CD4063BMS devices may be cascaded by connecting the outputs of the less significant comparator to the corresponding cascading inputs of the more significant comparator. Cascading inputs (A < B, A = B, and A > B) on the least significant comparator are connected to a low, a high, and a low level, respectively.