封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | CFP |

| Pkg. Code: | KBG |

| Lead Count (#): | 16 |

| Pkg. Dimensions (mm): | 10.4 x 6.9 x 0.00 |

| Pitch (mm): | 1.3 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pb (Lead) Free | Exempt |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | CFP |

| Lead Count (#) | 16 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | Not Applicable |

| Pitch (mm) | 1.3 |

| Pkg. Dimensions (mm) | 10.4 x 6.9 x 0.00 |

| DLA SMD | 5962R9665601VXC |

| Pb (Lead) Free | Exempt |

| Pb Free Category | Gold Plate over compliant Undercoat-e4 |

| MOQ | 25 |

| Temp. Range (°C) | -55 to +125°C |

| DSEE (MeV·cm2/mg) | 75 |

| Length (mm) | 10.4 |

| Qualification Level | QML Class V (space) |

| Rating | Space |

| TID HDR (krad(Si)) | 100 |

| TID LDR (krad(Si)) | ELDRS free |

| Width (mm) | 6.9 |

有关 CD4076BMS 的资源

描述

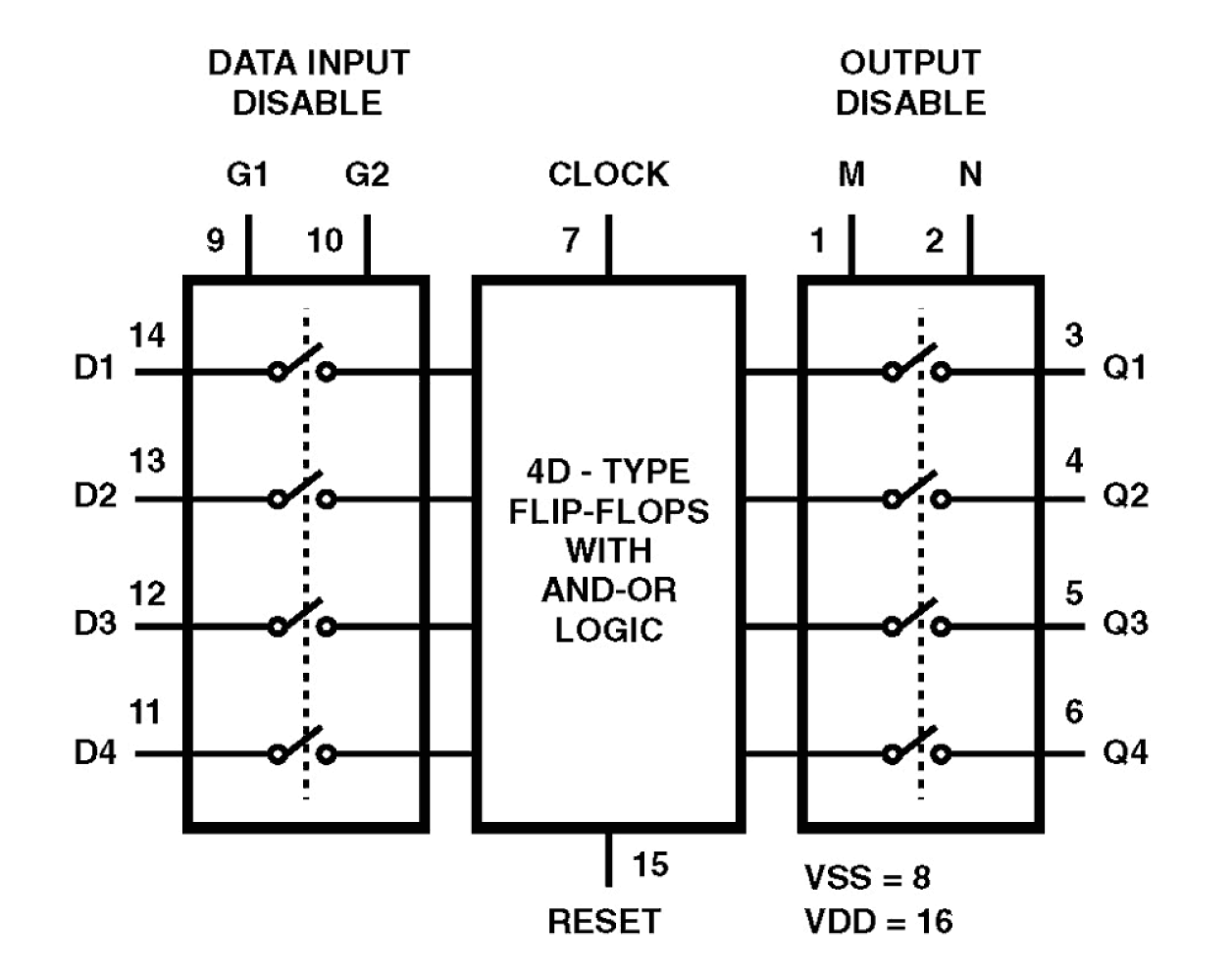

The CD4076BMS types are four-bit registers consisting of D-Type flip-flops that feature three-state outputs. Data Disable inputs are provided to control the entry of data into the flip-flops. When both Data Disable inputs are low, data at the D inputs are loaded into their respective flip-flops on the next positive transition of the clock input. Output Disable inputs are also provided. When the Output Disable inputs are both low, the normal logic states of the four outputs are available to the load. The outputs are disabled independently of the clock by a high logic level at either Output Disable input and present a high impedance. The CD4076BMS is supplied in these 16-lead outline packages: Braze Seal DIP H4T, Frit Seal DIP H1E and Ceramic Flatpack H6W.