特性

- PCIe Gen5 附加相位抖动:6fs RMS

- PCIe Gen6 附加相位抖动:4fs RMS

- PCIe Gen7 附加相位抖动:2.6fs RMS

- DB2000Q附加相位抖动:10fs RMS

- 12kHz 至 20MHz附加相位抖动:156.25MHz 时为 33fs RMS

- 掉电耐受(PDT)输入

- 灵活的启动時序(FSS)

- 丢失 CLKIN 时的自动时钟驻留(ACP)

- 展頻耐受性

- CLKIN 相容 HCSL 或 LVDS 信号电平

- -40 °C 至 +105 °C,1.8V ± 5% 工作溫度和電壓

- 可透過引脚或 SMBus 选擇:

- 33Ω、85Ω 或 100Ω 差分输出阻抗

- Output slew rate 输出信號斜率

- 输出振幅(A001 后缀)

- 9 个 SMBus 地址和誤写保护

描述

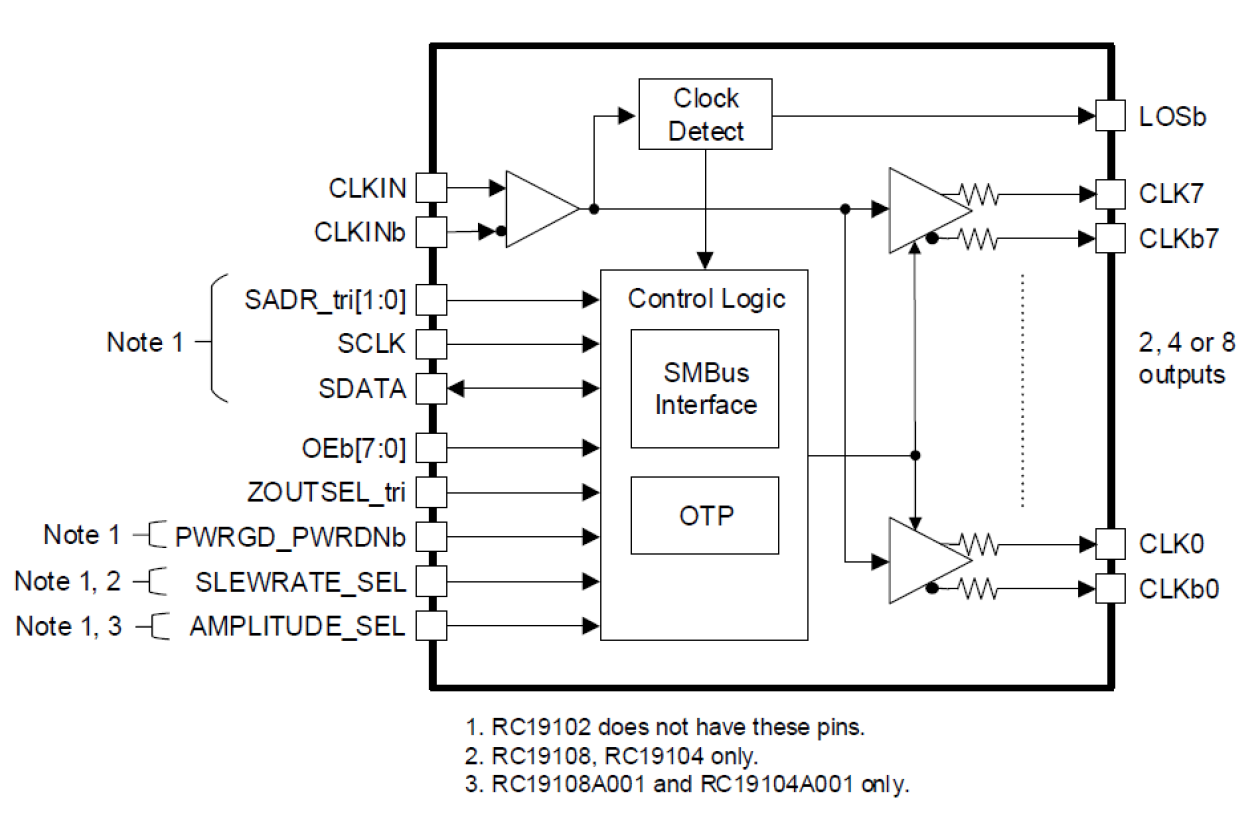

RC19108 是一个 1.8V 的 8 输出 PCIe Gen7 缓冲器,向下兼容早期的 PCIe 产品。 RC19108 提供超低的附加抖动並減少輸入對輸出的延迟時間,以获得更好的设计裕量并结合了多种功能,可实现更簡單和稳健的设计。

产品参数

| 属性 | 值 |

|---|---|

| Diff. Outputs | 8 |

| Diff. Output Signaling | LP-HCSL |

| Output Freq Range (MHz) | 1 - 400 |

| Diff. Inputs | 1 |

| Power Consumption Typ (mW) | 170 |

| Supply Voltage (V) | 1.8 - 1.8 |

| Output Type | LP-HCSL |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 1 - 400 |

| Additive Phase Jitter Typ RMS (fs) | 33 |

| Function | Fanout Buffer |

| Input Type | LVDS, HCSL |

| Output Banks (#) | 1 |

| Core Voltage (V) | 1.8V, 1.8V |

| Output Voltage (V) | 0.8 |

| Product Category | Clock Buffers & Drivers, PCI Express Clocks |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 5.0 x 5.0 x 0.9 | 40 | 0.4 |

产品对比

| RC19108A | 9DBL0851 | 9ZXL0851E | RC19008 | |

| Core Voltage (V) | 1.8 | 3.3 | 3.3 | 3.3 |

| Output Impedance | 34, 85, 100 | 85 | 85 | 85, 100 |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5, PCIe Gen6, PCIe Gen7 | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5 | 25G EDR, DB2000Q, IF-UPI, PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5, QPI, UPI | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5, PCIe Gen6, PCIe Gen7 |

| VOUT Slew-rate Control | Yes | No | No | Yes |

| Additive Jitter | 4fs | 13fs | - | 4fs |

| VOUT Amplitude Control | Yes | No | No | No |

应用

- 云和高性能计算

- nVME 存储

- 网络

- 加速器

当前筛选条件