特性

- Jitter below 100fs RMS maximum (10Hz to 20MHz)

- PLL core consists of fractional-feedback Analog PLL (APLL)

- Operates from a 25MHz to 80MHz crystal or XO

- APLL frequency independent of input / crystal frequency

- Operates as a frequency synthesizer or Digitally Controlled Oscillator (DCO)

- DCO has tuning granularity of < 1ppb

- Programmable status output

- 4 differential / 8 LVCMOS outputs

- Any frequency from 10MHz to 1GHz (180MHz for LVCMOS)

- Programmable output buffer supports HCSL (DC-coupled), LVDS/LVPECL/CML (AC-coupled) or two LVCMOS

- Differential output swing is selectable: 400mV to 800mV

- Output clock phase individually adjustable in 100ps steps

- Output Enable input with programmable effect

- Supports up to 1MHz I2C or up to 20MHz SPI serial processor port

- Can configure itself automatically after reset via internal customer-definable One-Time Programmable (OTP) memory with up to four different configurations

- 4 × 4 mm 24-VFQFPN package

描述

The RC22504A is a small, low-power timing component designed to be placed immediately adjacent to a PHY, switch, ASIC or FPGA that requires several reference clocks with jitter performance less than 100fs (max). The RC22504A can act as a frequency synthesizer to locally generate the reference clock or as a DCO for frequency margining or OTN clock applications.

此为出厂可配置设备。

试用自定义部件配置工具。

试用自定义部件配置工具。

产品参数

| 属性 | 值 |

|---|---|

| Diff. Outputs | 4 |

| Outputs (#) | 4 |

| Output Type | LVCMOS, HCSL, LVDS |

| Output Freq Range (MHz) | 10 - 1000 |

| Input Freq (MHz) | 25 - 312.5 |

| Inputs (#) | 2 |

| Input Type | Crystal, HCSL, LVDS, LVCMOS |

| Output Banks (#) | 4 |

| Core Voltage (V) | 1.8V, 3.3V |

| Output Voltage (V) | 1.8 |

| Feedback Input | No |

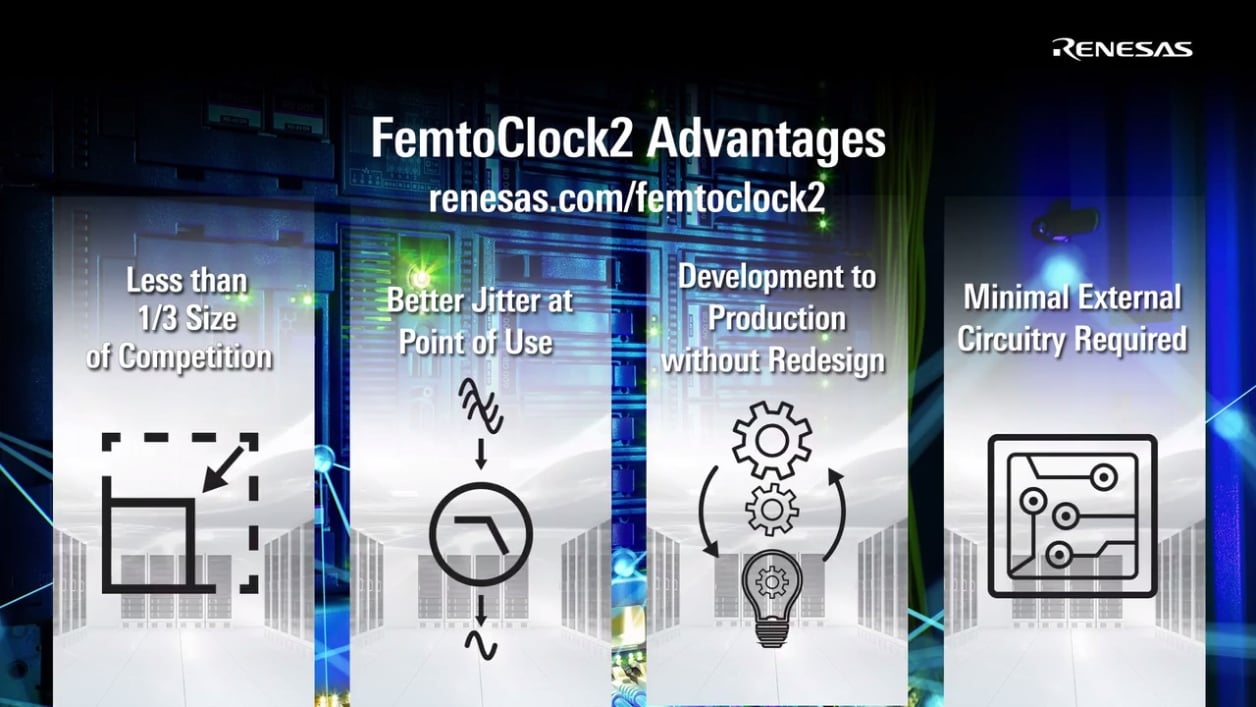

| Product Category | FemtoClock 2, Ultra-Low Jitter Clocks (<300 fs RMS), Extreme Performance Clocks (<150 fs RMS), Network Synchronization, PDH and SONET/SDH Clocks, Programmable Clocks |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 4.0 x 4.0 x 0.8 | 24 | 0.5 |