特性

- 1.0/1.5/2.0Gsps maximum output update rate

- 1Gsps maximum baseband input data rate

- 1, 2, or 4 configurable JESD204B serial input lanes running up to 10Gbps with embedded termination and programmable equalization

- JEDEC JESD204B device subclass I compliant: SYSREF-based deterministic and repeatable interface latency

- MDS enabling multiple DAC output streams being sample-level synchronized and phase coherent at the system-level

- Clock divider by 2,4,6,8 available at the input of the clock path with group delay compensation

- RF enable/disable pin and RF automatic mute for PA protection

- Power consumption 450mW per channel at 1.5Gsps

- Output common mode voltage 0.5V typical

- Typical dynamics performances: SFDR = 85dBc; IMD3= 85dBc; NSD = -164dBm/Hz

- Xilinx LogiCORE IP JESD204

- See: Altera JESD204B Reference Designs

描述

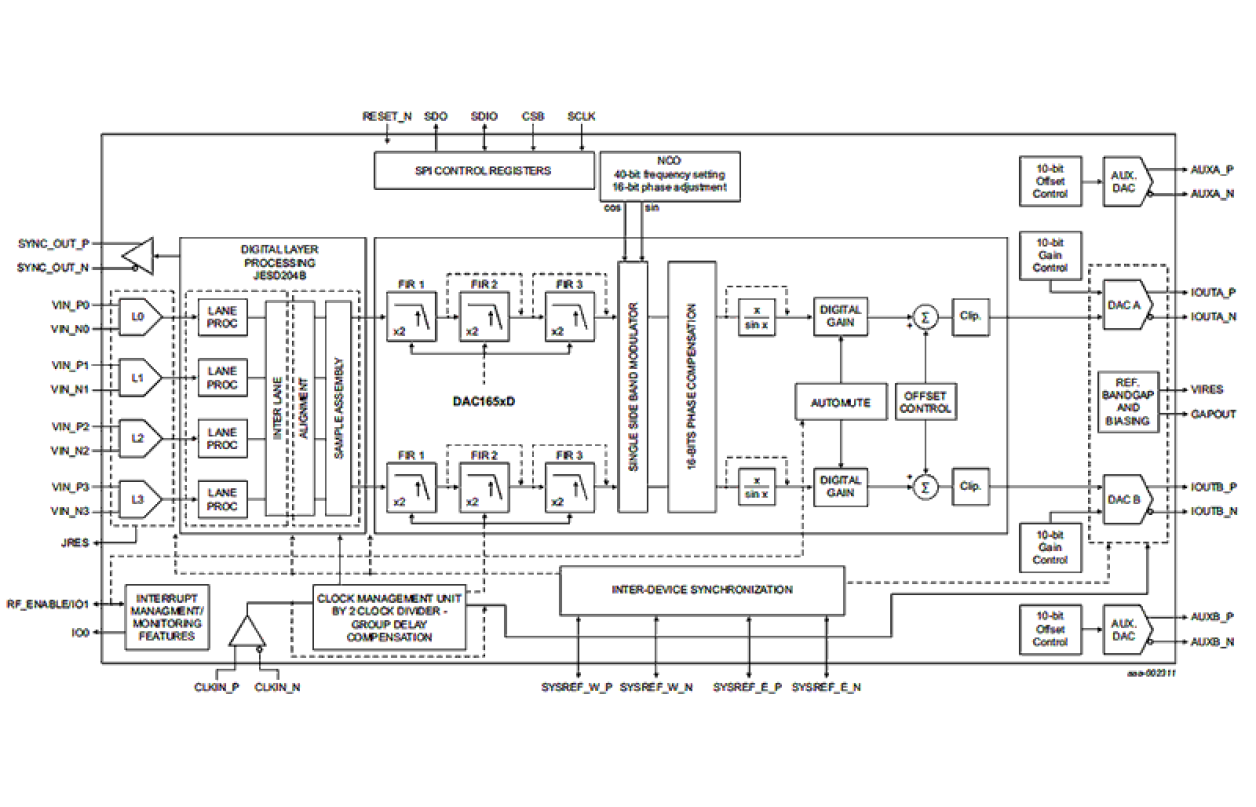

The DAC1653D is a high-speed, high-performance 16-bit dual-channel digital-to-analog converter (DAC). The device provides sample rates up to 2.0Gsps with selectable 2x, 4x, and 8x interpolation filters optimized for multi-carrier and broadband wireless transmitters. The DAC165xD integrates a JEDEC JESD204B compliant high-speed serial input data interface running up to 10Gbps allowing dual-channel input sampling at up to 1Gsps over four differential lanes. It offers numerous advantages over traditional parallel digital interfaces.

当前筛选条件