特性

- Dual 1:5 differential clock distribution

- 30 ps maximum device skew

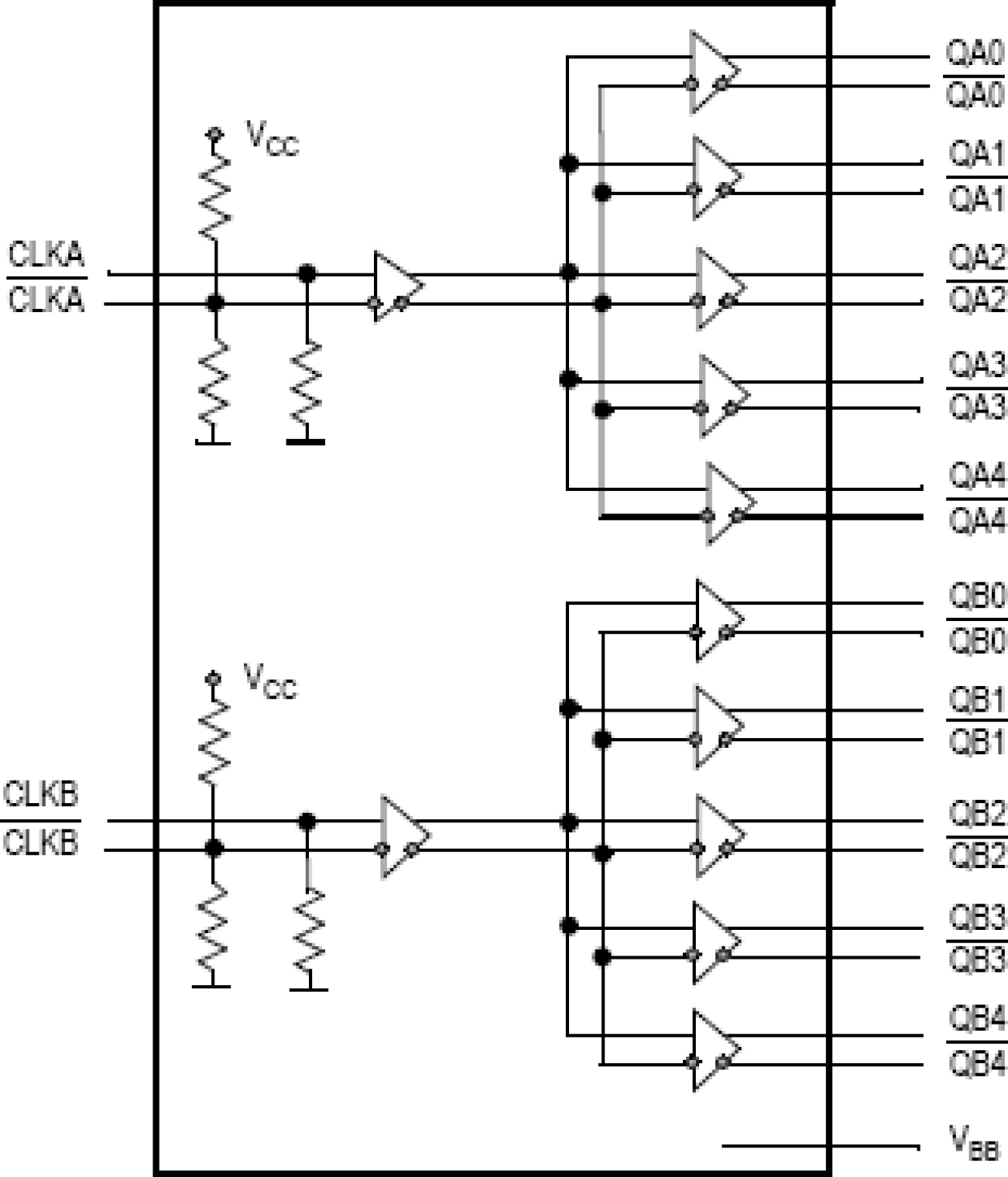

- Fully differential architecture from input to all outputs

- SiGe technology supports near-zero output skew

- Supports DC to 3GHz operation of clock or data signals

- ECL/PECL compatible differential clock outputs

- ECL/PECL compatible differential clock inputs

- Single 3.3V, –3.3V, 2.5V or –2.5V supply

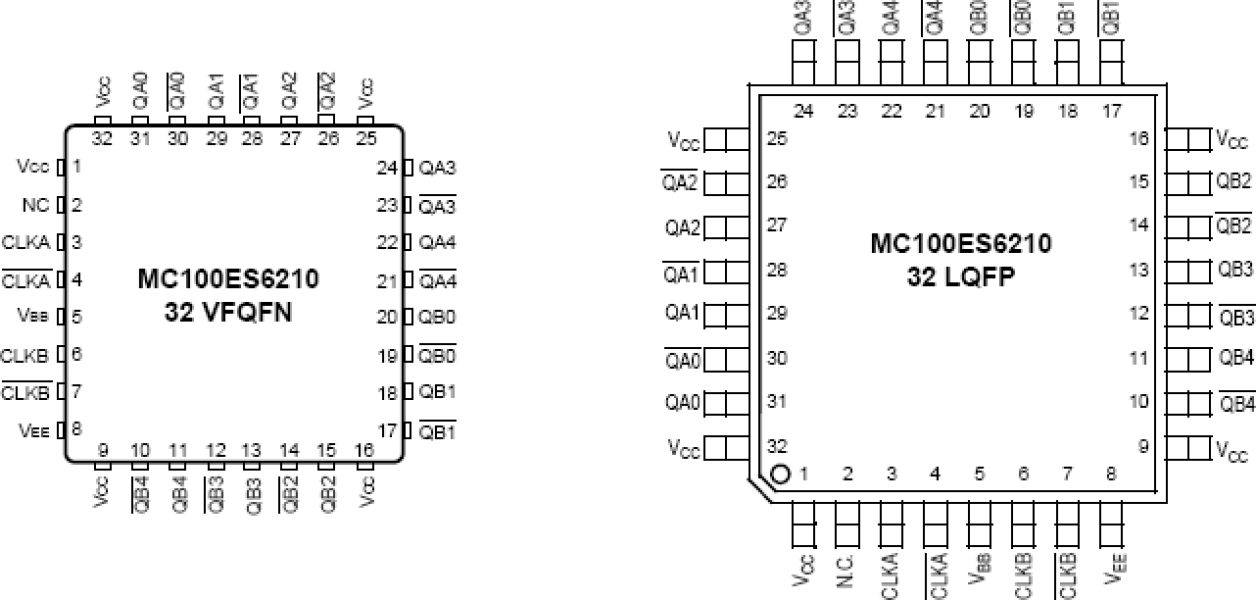

- Standard 32 lead LQFP and VFQFN packages

- Industrial temperature range

- Pin and function compatible to the MC100EP210

- 32-lead Pb-free Package Available

描述

The MC100ES6210 is designed for low skew clock distribution systems and supports clock frequencies up to 3GHz. The device consists of two independent 1:5 clock fanout buffers. The input signal of each fanout buffer is distributed to five identical, differential ECL/ PECL outputs. Both CLKA and CLKB inputs can be driven by ECL/PECL compatible signals. If VBB is connected to the CLKA or CLKB input and bypassed to GND by a 10nF capacitor, the MC100ES6210 can be driven by single-ended ECL/PECL signals utilizing the VBB bias voltage output. In order to meet the tight skew specification of the device, both outputs of a differential output pair should be terminated, even if only one output is used. In the case where not all ten outputs are used, the output pairs on the same package side as the parts being used on that side should be terminated. The MC100ES6210 can be operated from a single 3.3V or 2.5V supply. As most other ECL compatible devices, the MC100ES6210 supports positive (PECL) and negative (ECL) supplies. The is function and pin compatible to the MC100EP210.

当前筛选条件