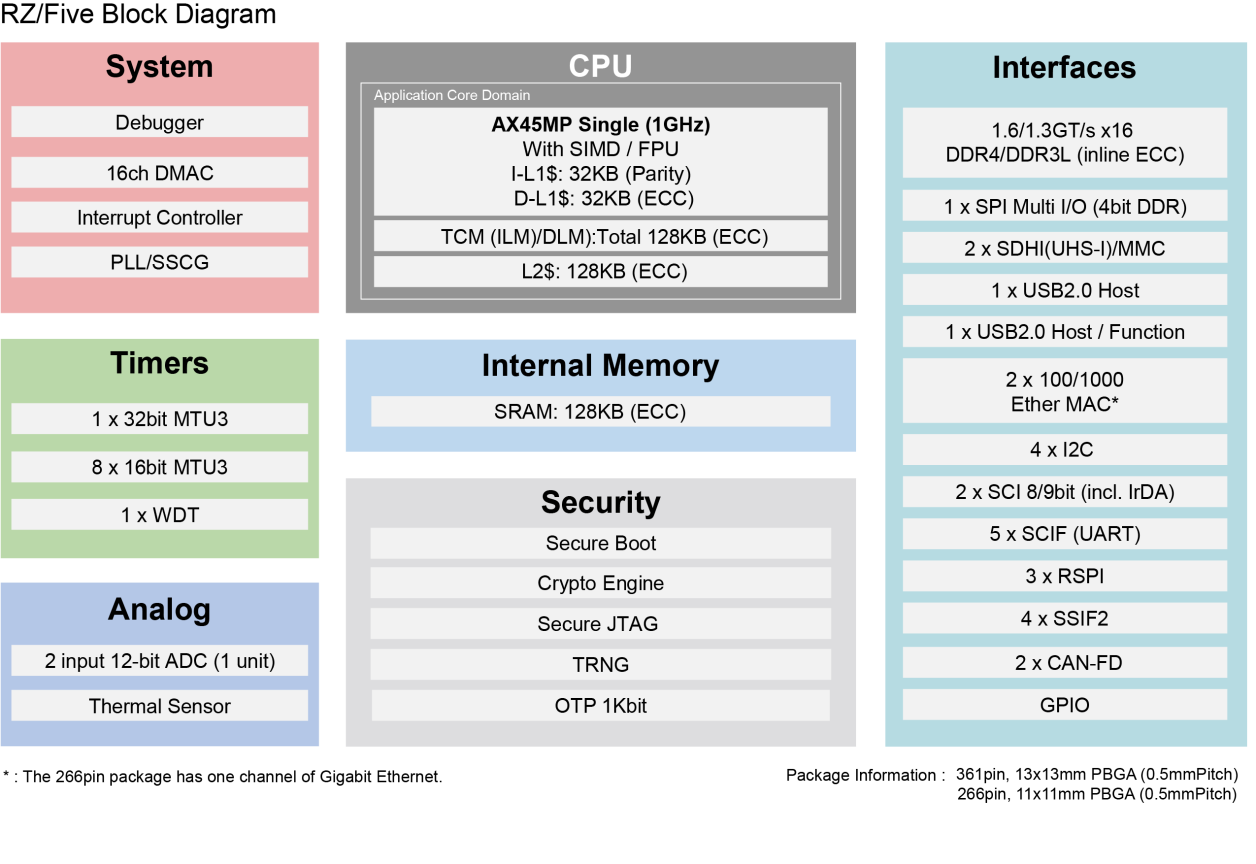

特性

- 64 位 RISC-V/AX45MP(单核)

- DDR4 或 DDR3L 内存接口

- 内存检错/纠错 (ECC)

- 千兆以太网接口 × 2

- CAN 接口(CAN-FD)× 2

- USB 2.0 接口 × 2

- SD 接口 × 2

- AD 转换器 × 2

- 13 x 13mm BGA 封装,11 x 11mm BGA 封装

描述

RZ/Five 微处理器包括 RISC-V CPU 内核 (AX45MP Single) 1.0 GHz,16 位 DDR3L/DDR4 接口。 此外,这款微处理器还配备有大量接口,如 Gbit-Ether、CAN 和 USB 2.0,因此特别适用于入门级社会基础设施网关控制和工业网关控制等应用。

有两种封装可选。 请参考 RZ/Five 概述,以了解每种封装所支持的功能差异。

13 x 13 mm 封装产品型号: R9A07G043F01GBG#BC0

11 x 11 mm 封装产品型号: R9A07G043F00GBG#BC0

RZ/Five 13 x 13 mm 封装还与 RZ/G2UL(类型 1)引脚兼容。

产品参数

| 属性 | 值 |

|---|---|

| CPU Architecture | RISC-V |

| Main CPU | RISC-V (AX45MP Single) |

| Program Memory (KB) | 0 |

| RAM (KB) | 128 |

| Carrier Type | Bulk (Tray), Full Carton (Tray) |

| Supply Voltage (V) | 2.97 - 3.63 |

| I/O Ports | 65, 114 |

| NPU | No |

| DRAM I/F | DDR3L-1333, DDR4-1600 (16-bit) |

| 3D GPU | No |

| Temp. Range (°C) | Ta = -40 to +85 |

| Operating Freq (Max) (MHz) | 1000 |

| Ethernet speed | 10M/100M/1G |

| Ethernet (ch) | 1, 2 |

| EtherCat (ch) (#) | 0 |

| USB FS (host ch/device ch) | ( 2 / 2 ) |

| USB HS (host ch/device ch) | ( 2 / 2 ) |

| USB SS (host ch/device ch) | ( 0 / 0 ) |

| PCI Express (generation and ch) | No |

| SCI or UART (ch) | 7 |

| SPI (ch) | 3 |

| I2C (#) | 4 |

| CAN (ch) | 2 |

| CAN-FD (ch) | 2 |

| Wireless | No |

| SDHI (ch) | 2 |

| High Resolution Output Timer | No |

| PWM Output (pin#) | 0 |

| 32-Bit Timer (ch) | 4 |

| 16-Bit Timer (ch) (#) | 8 |

| 8-Bit Timer (ch) | 0 |

| Standby operable timer | No |

| Asynchronous General Purpose Timer / Interval Timer (ch) | 0 |

| 16-Bit A/D Converter (ch) | 0 |

| 14-Bit A/D Converter (ch) | 0 |

| 12-Bit A/D Converter (ch) | 2 |

| 10-Bit A/D Converter (ch) | 0 |

| 24-Bit Sigma-Delta A/D Converter (ch) | 0 |

| 16-Bit D/A Converter (ch) | 0 |

| 12-Bit D/A Converter (ch) | 0 |

| 10-Bit D/A Converter (ch) (#) | 0 |

| 8-Bit D/A Converter (ch) | 0 |

| Capacitive Touch Sensing Unit (ch) | 0 |

| Graphics LCD Controller | No |

| MIPI Interfaces (DSI) (ch) | 0 |

| MIPI Interfaces (CSI) (ch) | 0 |

| Image Codec | No |

| Segment LCD Controller | No |

| Security & Encryption | No, Secure boot,AES,RSA,ECC,Hash,TRNG |

产品对比

| RZ/Five | RZ/G2UL | |

| CPU | RISC-V (AX45MP Single) | Cortex-A55 x 1 + Cortex-M33 x 1 |

| Lead Count (#) | 266, 361 | 361 |

| Operating Freq (Max) (MHz) | 1000 | 1000 |

| Ethernet Remarks | Gigabit Ethernet: 2ch or 1ch | Gigabit Ethernet: 2ch or 1ch |

| CAN (ch) | 2 | 2 |

| Display Function Remarks | Display Function: No | Parallel Interface |

应用方框图

| 可扩展 SMARC 2.1 网关 SoM,采用 RISC-V MPU 适用于 IIoT 网关的可扩展 SMARC 2.1 SoM 设计,具有低功耗、强大的连接性和灵活性。 |

其他应用

- 物联网网关

- 工业网关

当前筛选条件

加载中

筛选

软件与工具

样例程序

模拟模型

RZ/Five provides a new platform for high-performance IoT Edge solutions. Learn the advantages of RISC-V CPU, and how to easily scale development across RISC-V and Arm cores.

RZ/Five offers developers a new CPU option, enabling seamless scaling across RISC-V and Arm® cores to boost product development efficiency.

Related Resources

新闻和博客

博客 2023年7月26日 |

博客 2022年9月16日 |

新闻 2022年3月1日 |