封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | SOIC |

| Pkg. Code: | PSG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 12.8 x 7.6 x 2.34 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 37 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Abs. Pull Range Min. (± PPM) | 115 |

| App Jitter Compliance | TR62411, ETS300011, GR-1244 |

| Core Voltage (V) | 3.3V |

| Feedback Input | No |

| Input Freq (MHz) | 0.008 - 0.008, 10 - 50 |

| Input Type | LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 12.8 |

| MOQ | 74 |

| Output Banks (#) | 3 |

| Output Freq Range (MHz) | 0.008 - 51.84 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3V |

| Outputs (#) | 3 |

| Package Area (mm²) | 97.3 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 12.8 x 7.6 x 2.34 |

| Pkg. Type | SOIC |

| Product Category | Jitter Attenuators |

| Prog. Clock | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 2.34 |

| Width (mm) | 7.6 |

有关 MK2049-45 的资源

描述

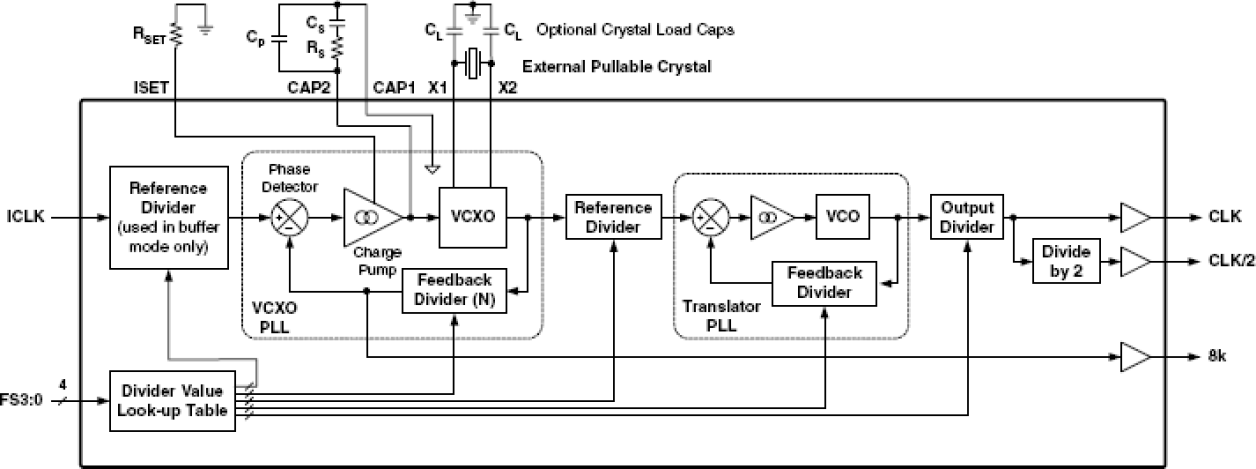

The MK2049-45 is a dual Phase-Locked Loop (PLL) device which can provide frequency synthesis and jitter attenuation. The first PLL is VCXO based and uses a pullable crystal to track signal wander and attenuate input jitter. The second PLL is a translator for frequency multiplication. Basic configuration is determined by a Mode/Frequency Selection Table. Loop bandwidth and damping factor are programmable via external loop filter component selection. Buffer Mode accepts a 10 to 50MHz input and will provide a jitter attenuated output at 0.5 x ICLK, 1 x ICLK or 2 x ICLK. In this mode the MK2049-45 is ideal for filtering jitter from high frequency clocks. In External Mode, ICLK accepts an 8 kHz clock and will produce output frequencies from a table of common communications clock rates, CLK and CLK/2. This allows for the generation of clocks frequency-locked to an 8 kHz backplane clock, simplifying clock synchronization in communications systems. The MK2049-45 can be dynamically switched between T1, E1, T3, E3 outputs with the same 24.576 MHz crystal. ICS can customize these devices for many other different frequencies. Contact your ICS representative for more details.