封装信息

| CAD 模型: | View CAD Model |

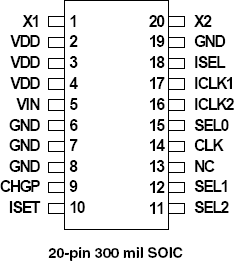

| Pkg. Type: | SOIC |

| Pkg. Code: | PSG20 |

| Lead Count (#): | 20 |

| Pkg. Dimensions (mm): | 12.8 x 7.6 x 2.34 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 1 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Lead Count (#) | 20 |

| Carrier Type | Tube |

| Moisture Sensitivity Level (MSL) | 1 |

| Qty. per Reel (#) | 0 |

| Qty. per Carrier (#) | 37 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Abs. Pull Range Min. (± PPM) | 115 |

| C-C Jitter Typ P-P (ps) | 150 |

| Core Voltage (V) | 3.3 |

| Feedback Input | No |

| Input Freq (MHz) | 0.0033 - 27 |

| Input Type | LVCMOS |

| Inputs (#) | 2 |

| Length (mm) | 12.8 |

| MOQ | 74 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 0.0033 - 27 |

| Output Type | LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 1 |

| Package Area (mm²) | 97.3 |

| Phase Jitter Typ RMS (ps) | 150 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 12.8 x 7.6 x 2.34 |

| Pkg. Type | SOIC |

| Prog. Clock | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Thickness (mm) | 2.34 |

| Width (mm) | 7.6 |

| 已发布 | No |

有关 MK2058-01 的资源

描述

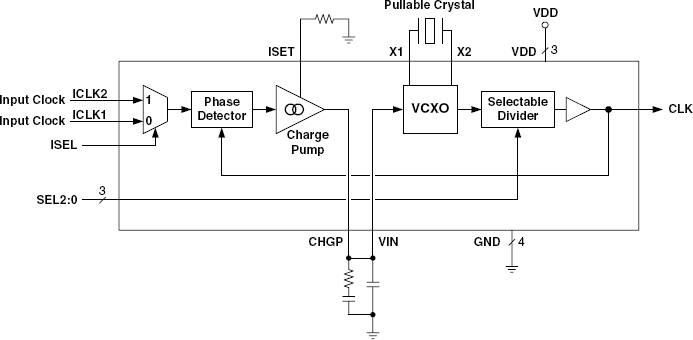

The MK2058-01 is a VCXO (Voltage Controlled Crystal Oscillator) based clock jitter attenuator designed for system clock distribution applications. This monolithic IC, combined with an external inexpensive quartz crystal, can be used to replace a more costly hybrid VCXO retiming module. The device accepts and outputs the same clock frequency in selectable ranges covering 4 kHz to 27 MHz. A dual input mux is also provided. By controlling the VCXO frequency within a phase-locked loop (PLL), the output clock is phase and frequency locked to the input clock. Through selection of external loop filter components, the PLL loop bandwidth and damping factor can be tailored to meet system clock requirements. A loop bandwidth down to the Hz range is possible.