封装信息

| Pkg. Type: | TQFP |

| Pkg. Code: | PRG32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 7.0 x 7.0 x 1.4 |

| Pitch (mm): | 0.8 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | TQFP |

| Lead Count (#) | 32 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tray |

| Advanced Features | Feedback Input |

| C-C Jitter Max P-P (ps) | 15 |

| Core Voltage (V) | 2.5V, 3.3V |

| Feedback Input | Yes |

| Input Freq (MHz) | 50 - 200 |

| Input Type | LVCMOS |

| Inputs (#) | 1 |

| Length (mm) | 7 |

| MOQ | 250 |

| Moisture Sensitivity Level (MSL) | 3 |

| Output Banks (#) | 1 |

| Output Freq Range (MHz) | 50 - 200 |

| Output Skew (ps) | 150 |

| Output Type | LVCMOS |

| Output Voltage (V) | 2.5V, 3.3V |

| Outputs (#) | 17 |

| Package Area (mm²) | 49 |

| Pb Free Category | e3 Sn |

| Period Jitter Max P-P (ps) | 10 |

| Period Jitter Typ P-P (ps) | 7 |

| Pitch (mm) | 0.8 |

| Pkg. Dimensions (mm) | 7.0 x 7.0 x 1.4 |

| Prog. Clock | No |

| Qty. per Carrier (#) | 250 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 7 |

有关 MPC961C 的资源

描述

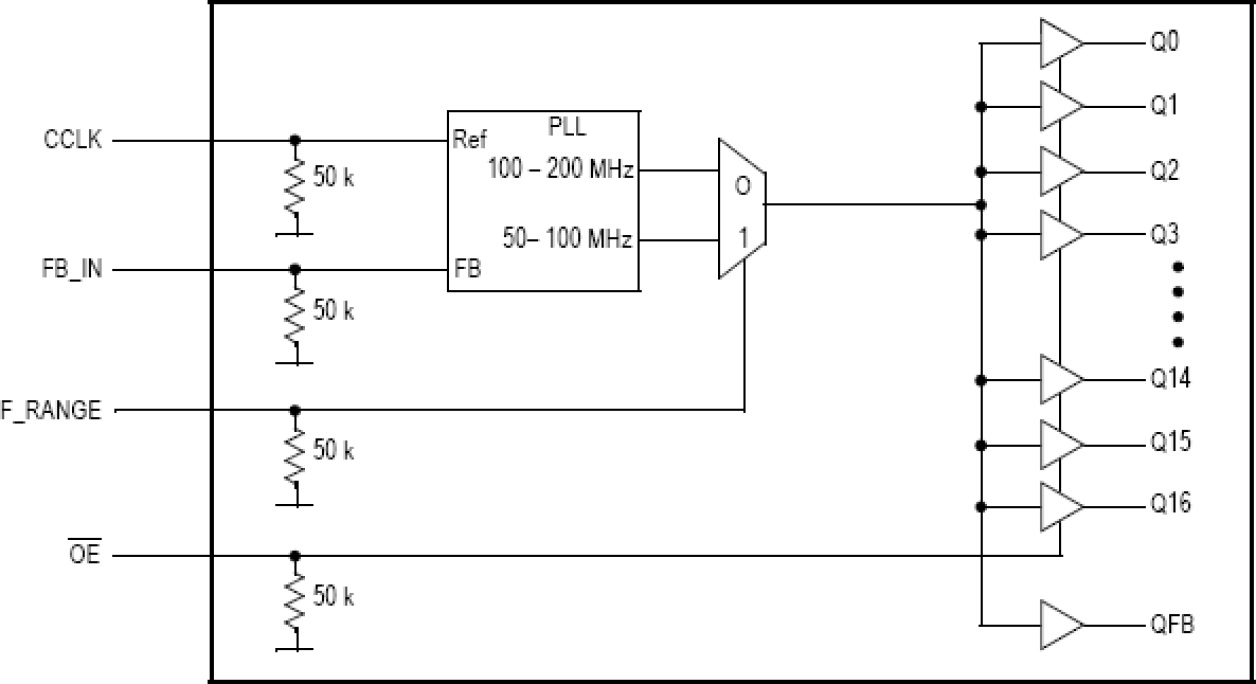

The MPC961 is offered with two different input configurations. The MPC961C offers an LVCMOS reference clock while the MPC961P offers an LVPECL reference clock. When pulled high the OE pin will force all of the outputs (except QFB) into a high impedance state. Because the OE pin does not affect the QFB output, down stream clocks can be disabled without the internal PLL losing lock. The MPC961 is fully 2.5 V or 3.3 V compatible and requires no external loop filter components. All control inputs accept LVCMOS compatible levels and the outputs provide low impedance LVCMOS outputs capable of driving terminated 50 ? transmission lines. For series terminated lines the MPC961 can drive two lines per output giving the device an effective fanout of 1:36. The device is packaged in a 32-lead LQFP.