特性

- 符合 PCIe Gen 1-7 标准

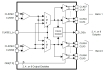

- 2:2 多路复用器或两个 1 路输出缓冲器选项

- 驱动源端接和双端接负载

- 可选 34Ω、85Ω 和 100Ω 输出阻抗

- 掉电容差 (PDT)

- 灵活的启动時序 (FSS)

- 自动时钟停车 (ACP)

- 专用 OE# 引脚用于控制组输出

- 3mm × 3mm 20-VFQFPN 封装

描述

RC19302 是一款1.8V的 2:2 PCIe Gen7 多路复用器,向下兼容早期 PCIe 产品。 RC19302 提供超低的附加抖动 並減少輸入對輸出的 延迟性能時間,以获得更好的设计裕量并结合了多种功能,可实现更簡單和稳健的设计。

产品参数

| 属性 | 值 |

|---|---|

| Temp. Range (°C) | -40 to 105°C |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| VFQFPN | 3.0 x 3.0 x 1.0 | 20 | 0.4 |

应用

- 云和高性能计算

- nVME 存储

- 网络

- 加速器

当前筛选条件

筛选

软件与工具

样例程序

模拟模型

The RC family consists of PCIe Gen7 clock buffer and multiplexer solutions, providing the industry's smallest and most compact footprint.

A detailed overview of IDT's full-featured PCI Express (PCIe) clock and timing solutions. The presentation addresses PCIe Gen 1, Gen 2, Gen 3, and Gen 4 architectures and how IDT's industry-leading solutions provide all the functions, features, and performance required by the application.

Presented by Ron Wade, System Architect at IDT. For more information visit the PCIe clocks page.

A brief overview of the PCI Express common clock (CC) jitter model, and the transfer functions as they relate to the timing PLLs. This model applies to PCI Express (PCIe) Gen 2, Gen 3, Gen 4 and Gen 5. The equations would be slightly different for other PCIe architectures, such as SRIS, SRnS, or data clocked.

Presented by Ron Wade, system architect at IDT (acquired by Renesas). For more information about Renesas's PCIe timing solutions, visit the PCI Express (PCIe) Clocks page.

This video compares PCIe Gen3–7 common clock jitter filters with a typical 12kHz to 20MHz plot to highlight the differences in filtering approaches.