封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | LGA |

| Pkg. Code: | LTW32 |

| Lead Count (#): | 32 |

| Pkg. Dimensions (mm): | 4.0 x 4.0 x 1.0 |

| Pitch (mm): | 0.4 |

环境和出口类别

| Moisture Sensitivity Level (MSL) | 3 |

| Pb (Lead) Free | Yes |

| ECCN (US) | EAR99 |

| HTS (US) | 8542.39.0090 |

产品属性

| Pkg. Type | LGA |

| Lead Count (#) | 32 |

| Carrier Type | Tray |

| Moisture Sensitivity Level (MSL) | 3 |

| Pkg. Dimensions (mm) | 4.0 x 4.0 x 1.0 |

| Qty. per Reel (#) | 0 |

| Diff. Outputs | 5 |

| Input Type | LVDS, LP-HCSL, LVCMOS |

| Qty. per Carrier (#) | 490 |

| Pb (Lead) Free | Yes |

| Pb Free Category | e3 Sn |

| Temp. Range (°C) | -40 to 85°C |

| Advanced Features | Programmable Clock |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5, PCIe Gen6, PCIe Gen7 |

| Application | Data Center Accelerators, Switches, Routers, Synchronous Ethernet |

| Architecture | Common, SRIS, SRNS |

| C-C Jitter Max P-P (ps) | 50 |

| Channels (#) | 1 |

| Core Voltage (V) | 1.8V, 2.5V, 3.3V |

| Diff. Inputs | 2 |

| Diff. Output Signaling | LP-HCSL, LVDS, LVPECL, LVCMOS |

| Family Name | VersaClock® 7 |

| Fractional Output Dividers (#) | 3 |

| Function | Generator |

| Input Freq (MHz) | 1 - 650 |

| Inputs (#) | 2 |

| Length (mm) | 4 |

| Longevity | 2040 四月 |

| MOQ | 490 |

| Output Freq Range (MHz) | 0.001 - 650 |

| Output Impedance | 85, 100 |

| Output Skew (ps) | 30 |

| Output Type | LVDS, LP-HCSL, LVCMOS |

| Output Voltage (V) | 1.8V, 2.5V, 3.3V |

| Phase Jitter Typ RMS (fs) | 150 |

| Phase Jitter Typ RMS (ps) | 0.15 |

| Pitch (mm) | 0.4 |

| Power Consumption Typ (mW) | 1000 |

| Product Category | VersaClock, Ultra-Low Jitter Clocks (<300 fs RMS), PCI Express Clocks, Programmable Clocks |

| Prog. Clock | Yes |

| Prog. Interface | OTP, I2C, SPI, SMBUS, EEPROM |

| Reference Output | No |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | Yes |

| Supply Voltage (V) | 1.8 - 1.8, 2.5 - 2.5, 3.3 - 3.3 |

| Tape & Reel | No |

| Thickness (mm) | 1 |

| Width (mm) | 4 |

有关 RC210 的资源

描述

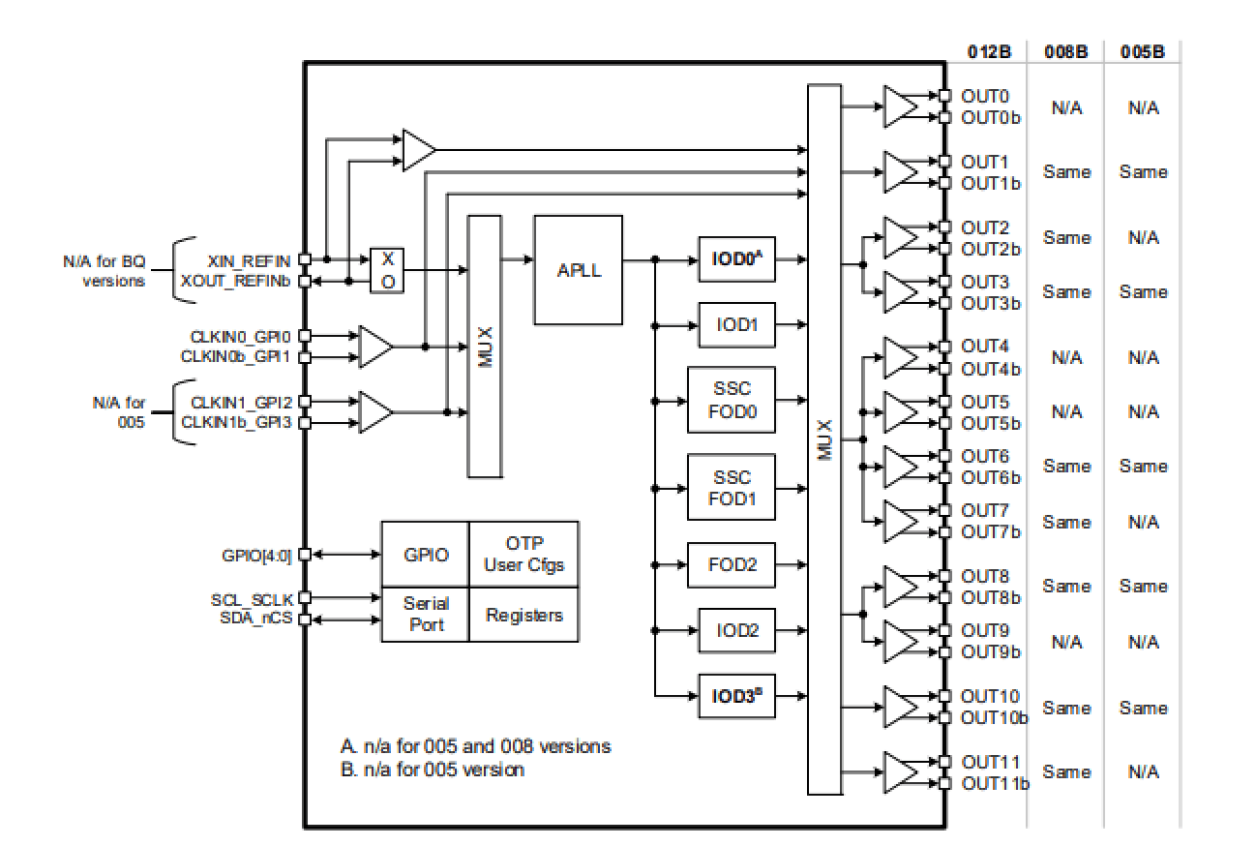

RC21xxxA(RC21012A 和 RC21008A)属于瑞萨电子的 VersaClock® 7 可编程时钟发生器系列。它适用于高性能计算、数据通信和工业应用,时钟晶片需紧靠 PHY、Switch、ASIC 或 FPGA以符合主晶片对抖动性能的要求,这些应用都需要具有 150fs 标准 RMS 抖动性能的参考时钟。

多达 27 种配置可在多种设计中重复使用,可储存在晶片上一次性可编程 (OTP) 储存器或外部 I2C EEPROM 中。也可以支持备用输入时钟,在需要时用作参考时钟。