特性

- 1.8V/2.5V/3.3V 灵活工作电压

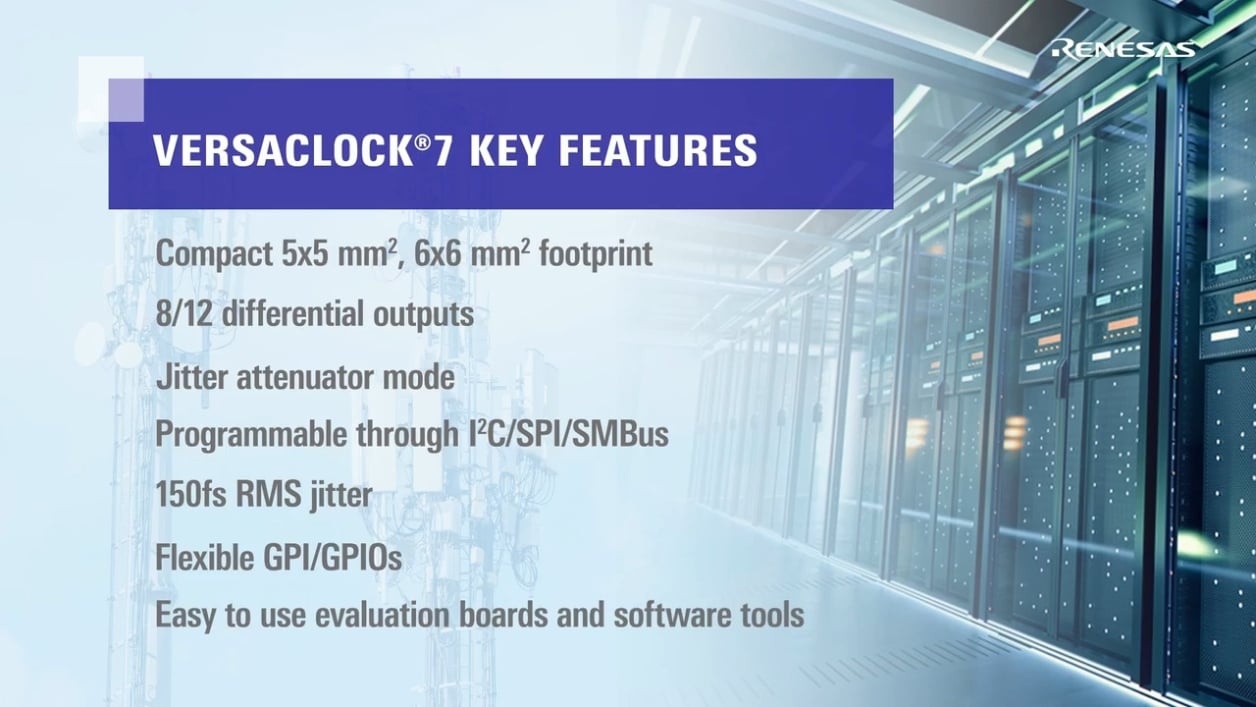

- 标准的 150fs RMS 12kHz-20MHz 相位抖动

- 具有集成震荡晶体 5/8/12 路输出的选项

- 1kHz-650MHz LVDS/LP-HCSL 输出

- 1kHz-200MHz LVCMOS 输出

- 可编程硬件配置选择引脚

- 符合 PCIe Gen 5/6/7 标准

- 节省空间的封装 4mm x 4mm、5mm x 5mm、6mm x 6mm

- 集成震荡晶体进而节省空间并实现 BOM 优化

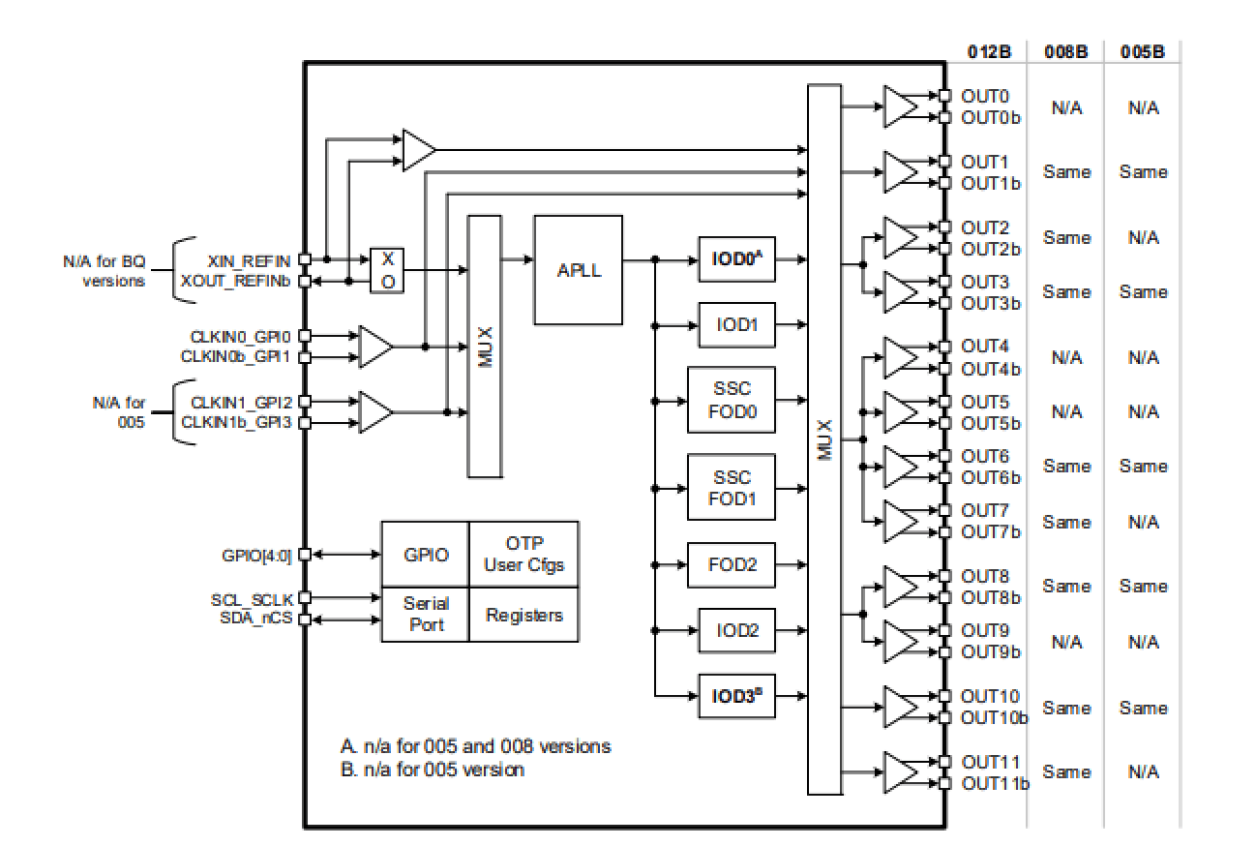

描述

RC21xxxA(RC21012A 和 RC21008A)属于瑞萨电子的 VersaClock® 7 可编程时钟发生器系列。它适用于高性能计算、数据通信和工业应用,时钟晶片需紧靠 PHY、Switch、ASIC 或 FPGA以符合主晶片对抖动性能的要求,这些应用都需要具有 150fs 标准 RMS 抖动性能的参考时钟。

多达 27 种配置可在多种设计中重复使用,可储存在晶片上一次性可编程 (OTP) 储存器或外部 I2C EEPROM 中。也可以支持备用输入时钟,在需要时用作参考时钟。

此为出厂可配置设备。

试用自定义部件配置工具。

试用自定义部件配置工具。

产品参数

| 属性 | 值 |

|---|---|

| Diff. Outputs | 5, 8, 12 |

| App Jitter Compliance | PCIe Gen1, PCIe Gen2, PCIe Gen3, PCIe Gen4, PCIe Gen5, PCIe Gen6, PCIe Gen7 |

| Outputs (#) | 16, 24 |

| Output Type | LVDS, LP-HCSL, LVCMOS |

| Output Freq Range (MHz) | 0.001 - 650 |

| Input Freq (MHz) | 1 - 650 |

| Inputs (#) | 2 |

| Input Type | LVDS, LP-HCSL, LVCMOS |

| Output Banks (#) | 6 |

| Core Voltage (V) | 1.8V, 2.5V, 3.3V |

| Output Voltage (V) | 1.8V, 2.5V, 3.3V |

| Product Category | VersaClock, Ultra-Low Jitter Clocks (<300 fs RMS), PCI Express Clocks, Programmable Clocks |

应用方框图

| 可重新配置的高性能时钟系统 可重新配置的时钟系统可实现精确同步、实时适应性和设计重用。 |

| AI 加速卡的电源与时钟系统 面向 AI 加速卡的高效率电源与定时系统,支持先进的 PCIe 时钟架构。 |

其他应用

- 高性能计算

- 数据中心加速器

- 交换机/路由器

- 同步以太网

- 工业