概览

描述

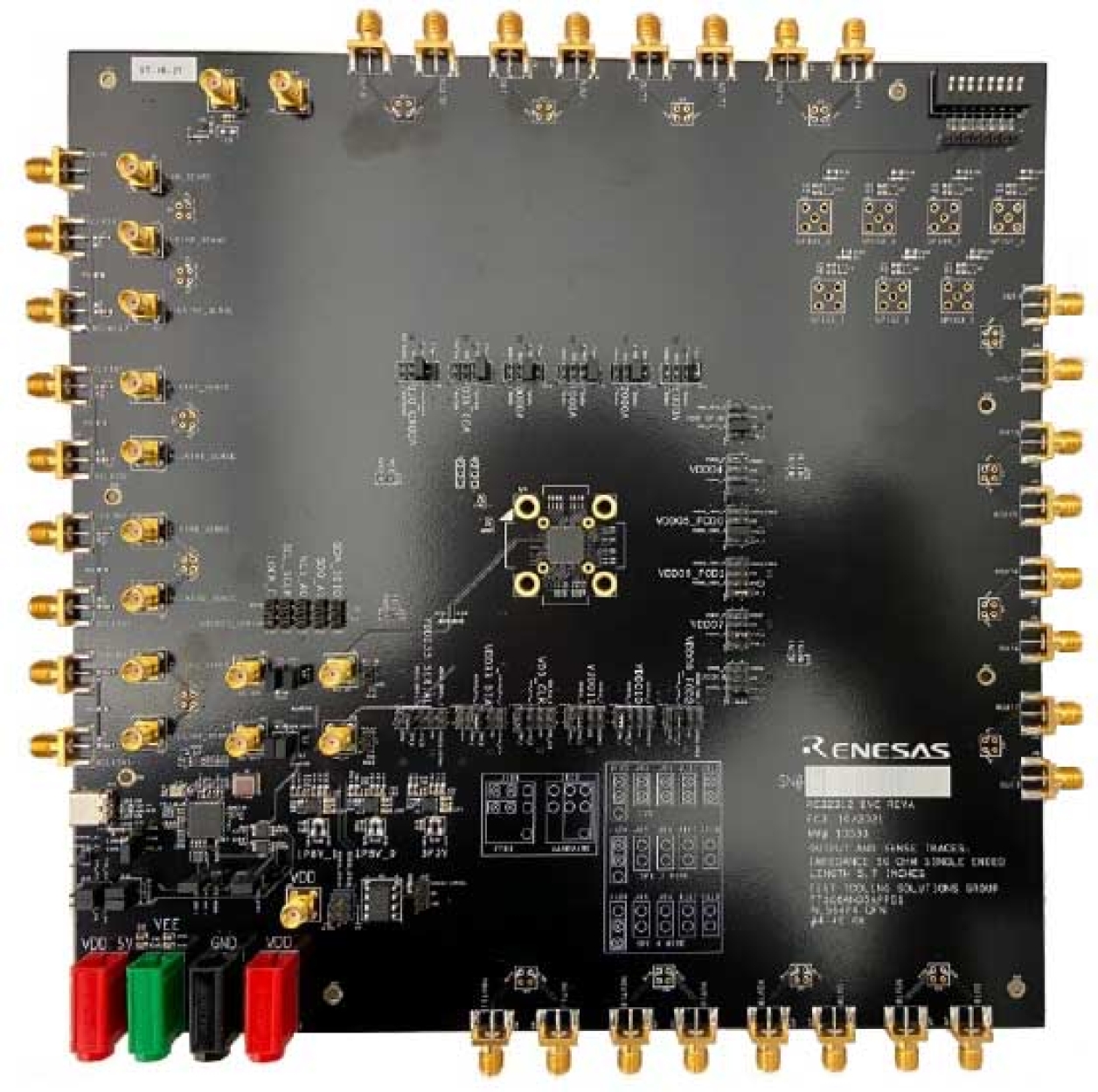

此 RC32312A-EVK 评测套件用于评测 RC32312A FemtoClock™ 3 抖动衰减器和时钟发生器。 RC32312A 可提供一个独立时钟域,可配置为数字锁相环(DPLL) 或数控振荡器 (DCO) ,并具有多达 4 个独立频率域,这些频域可以锁定到外部参考输入,或锁定到自由运行晶体或振荡器。 DPLL 通道符合同步以太网时钟要求,可用于抖动衰减和频率转换。 DCO 可进行编程来合成所需的频率,外部软件调整频率输出达到的最小分辨率为 1.11e-13。 DPLL 几乎可锁定到从 4kHz 到 1GHz 之间的任何频率,DPLL 和 DCO 几乎可生成从 4kHz 到 1GHz 之间的任何频率,抖动衰减器模式下,在 12kHz 到 20MHz 的范围内,典型均方根抖动低于 65fs,时钟合成器模式下,在 12kHz 到 20MHz 的范围内,典型均方根抖动低于 55fs RMS。

特性

- 四个差分时钟输入

- 十二个差分时钟输出

- 外部EEPROM 存储启动配置文件

- XIN 管脚灵活地连接用实验室信号发生器或 OCXO/TCXO/XO 组件和电路板

- 实验室电源连接器

- USB-C 电源

- 配置与寄存器读取串行端口

应用

设计和开发

视频和培训

Introducing the industry's lowest jitter 25fs RMS clock generator and jitter attenuator.