概览

描述

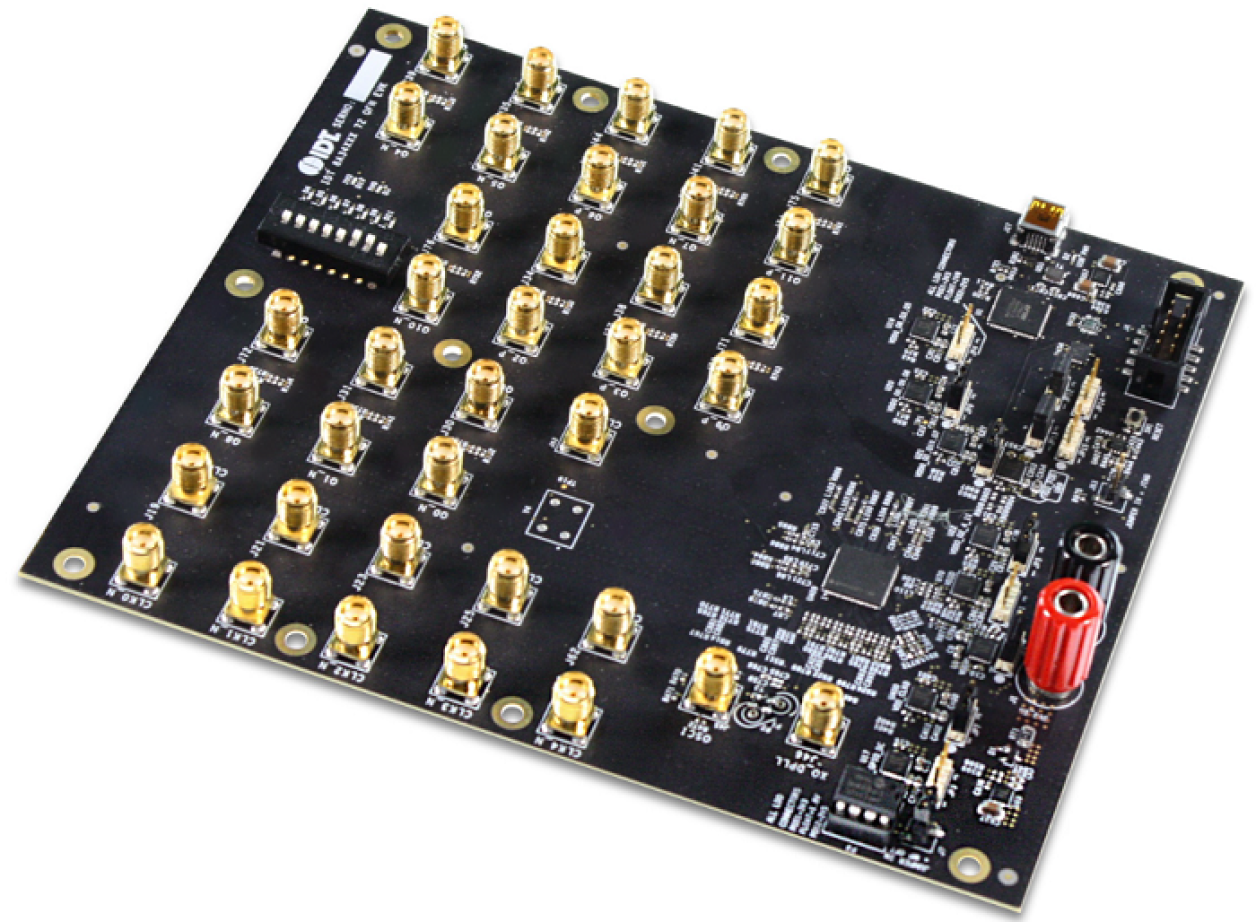

This is the evaluation kit for the Renesas RC38612 ClockMatrix Radio Access Network Equipment Synchronizer. This is the superset device and can also be used to evaluate the RC32012 device. The RC38612 provides six independent timing channels that can be configured as Digital PLLs (DPLLs) or as Digitally Controlled Oscillators (DCOs). The DPLL channels meet synchronous Ethernet and wireless radio clocking requirements and they can be used for jitter attenuation and frequency translation. The DCOs can be programmed to synthesize the desired frequency and can be steered by external software with resolution of 1.11E-16. The DPLLs can lock to virtually any frequency from 0.5Hz to 1GHz and the DPLLs and DCOs can generate virtually any frequency from 0.5Hz to 1GHz with typical jitter below 150fs RMS from 12kHz to 20MHz.

特性

- 5 differential clock inputs

- 12 differential outputs

- 2 serial port channels

- On-board EEPROM

- On-board miniOCXO

- 16 GPIO controls

- Selectable voltage controls