特性

- Meets or exceeds PC133 registered DIMM Specification 1.1

- Spread Spectrum Clock compatible

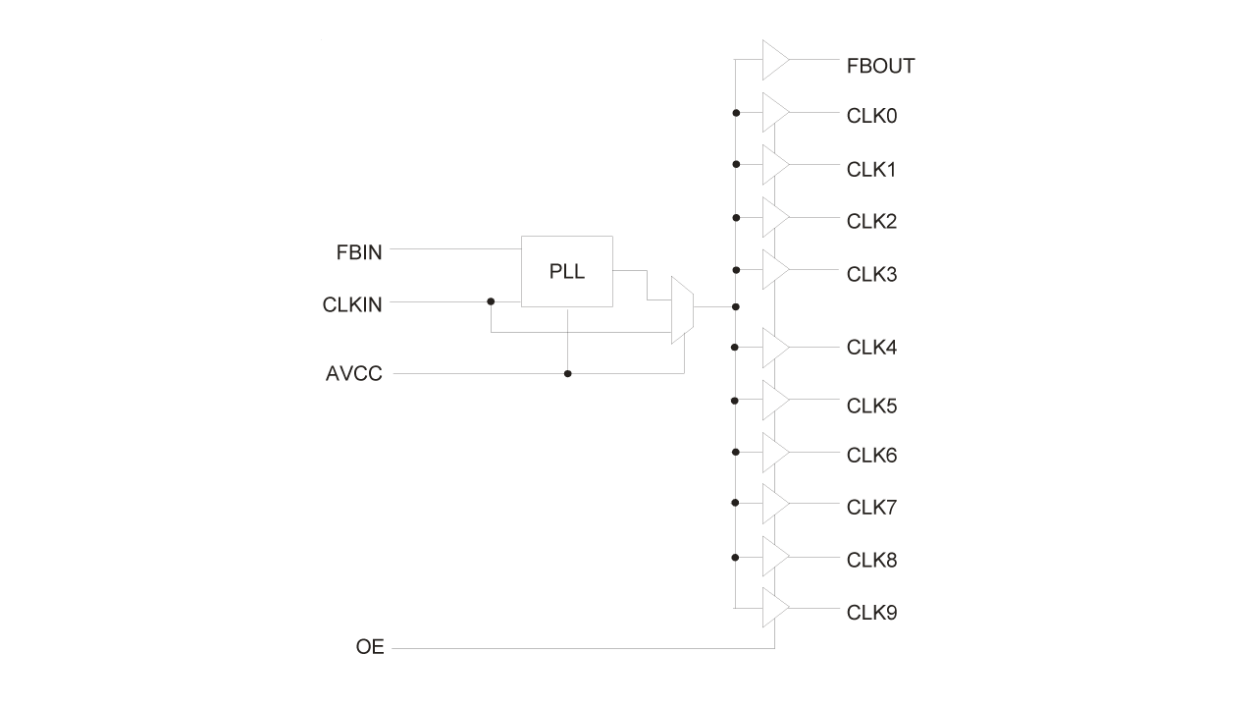

- Distributes one clock input to one bank of ten outputs

- Operating frequency 25MHz to 175MHz

- External feedback input (FBIN) terminal is used to synchronize the outputs to the clock input

- No external RC network required

- Operates at 3.3V VCC

- Plastic 24-pin 173mil TSSOP package

描述

The 2510C is a high-performance, low-skew, low-jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the CLKIN signal with the CLKOUT signal. It is specifically designed for use with synchronous SDRAMs. The 2510C operates at 3.3V VCC and drives up to ten clock loads.

产品参数

| 属性 | 值 |

|---|---|

| Pkg. Code | PGG24 |

| Length (mm) | 7.8 |

| Width (mm) | 4.4 |

| Temp. Grade | C |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TSSOP | 7.8 x 4.4 x 1.0 | 24 | 0.65 |

当前筛选条件