特性

- JEDEC Compliant RCD

- DDR4-1600/1866/2133/2400

- Optimized for JEDEC DDR4 2400 MT/s RDIMM, LRDIMM and UDIMM

- Designed to be used with IDT 4DB0226KA (DDR4 DB) and IDT TSE2004GB2 (DDR4 Temperature Sensor)

- Supports CKE Power Down operation modes

- Support Quad Chip Select Operation

- Direct Dual CS Mode

- Direct QuadCS Mode

- Encoded QuadCS Mode

- Pinout optimized DDR4 RDIMM, LRDIMM and UDIMM PCB layout

- Provides access to internal control words for configuring the device features and adapting in different RDIMM and system applications

- Available in 253-ball Dual-Pitch (0.50mm/0.65mm), 15 x 20 Grid , Rectangular Ball Grid Array Package

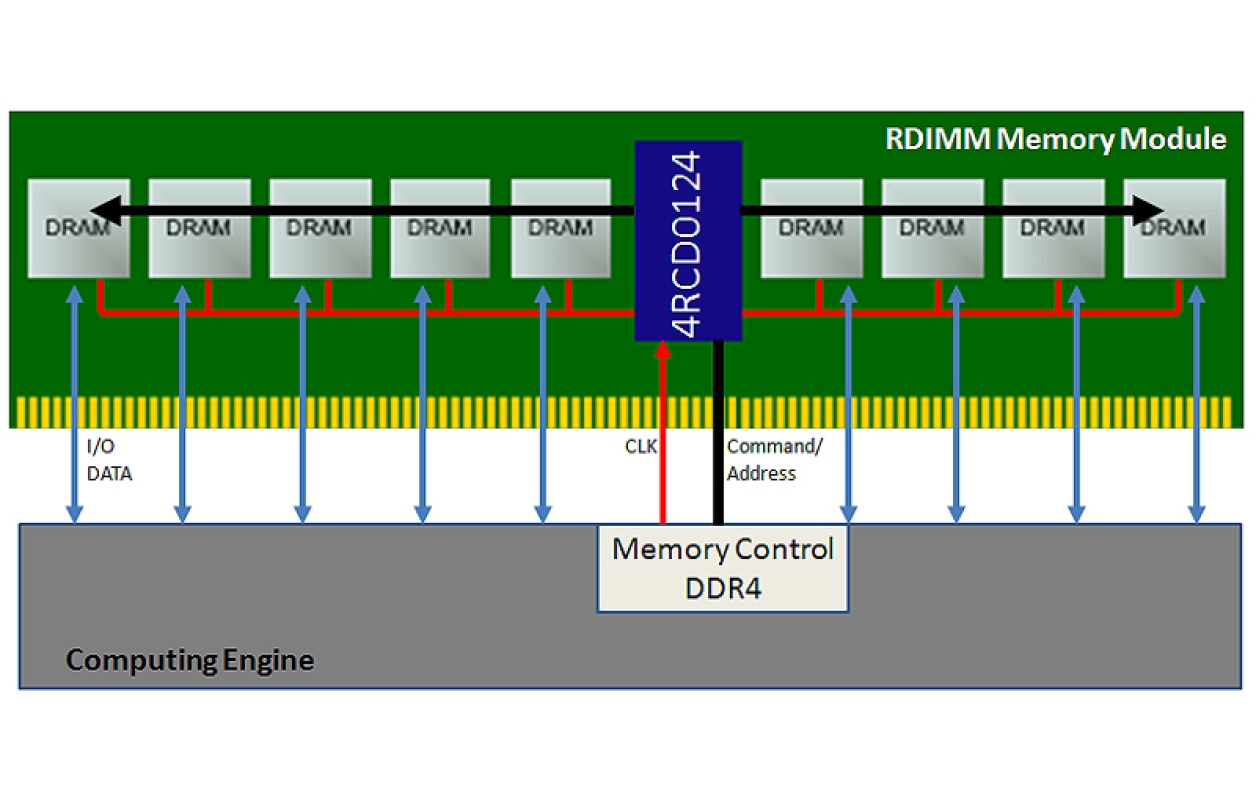

描述

IDT’s JEDEC-compliant 4RCD0124K is a Gen 1 DDR4 registered clock driver (RDC) for Enterprise Class Server RDIMMs, LRDIMMs and UDIMMs operating with a 1.2V Vdd supply. It features a 32-bit 1:2 register command, address buffer with parity designed for 1.2V VDD operation.

当前筛选条件