特性

- JEDEC-compliant RCD

- DDR4-1600/1866/2133/2400/2667/2933/3200

- Optimized for JEDEC DDR4 2667 MT/s RDIMM, LRDIMM, and UDIMM

- Designed to be used with 4DB0232KC (DDR4 Gen 2.5 data buffer) and TSE2004GB2C0 (DDR4 temperature sensor)

- Supports CKE power-down operation modes

- Support quad chip select operation

- Direct dual CS mode

- Direct quadCS mode

- Encoded quad CS mode

- Pinout-optimized DDR4 RDIMM, LRDIMM, and UDIMM PCB layout

- Provides access to internal control words for configuring the device features and adapting to different RDIMM and system applications

- Available in a 253-ball dual-pitch (0.50mm/0.65mm), 15 x 20 grid, rectangular ball grid array package

描述

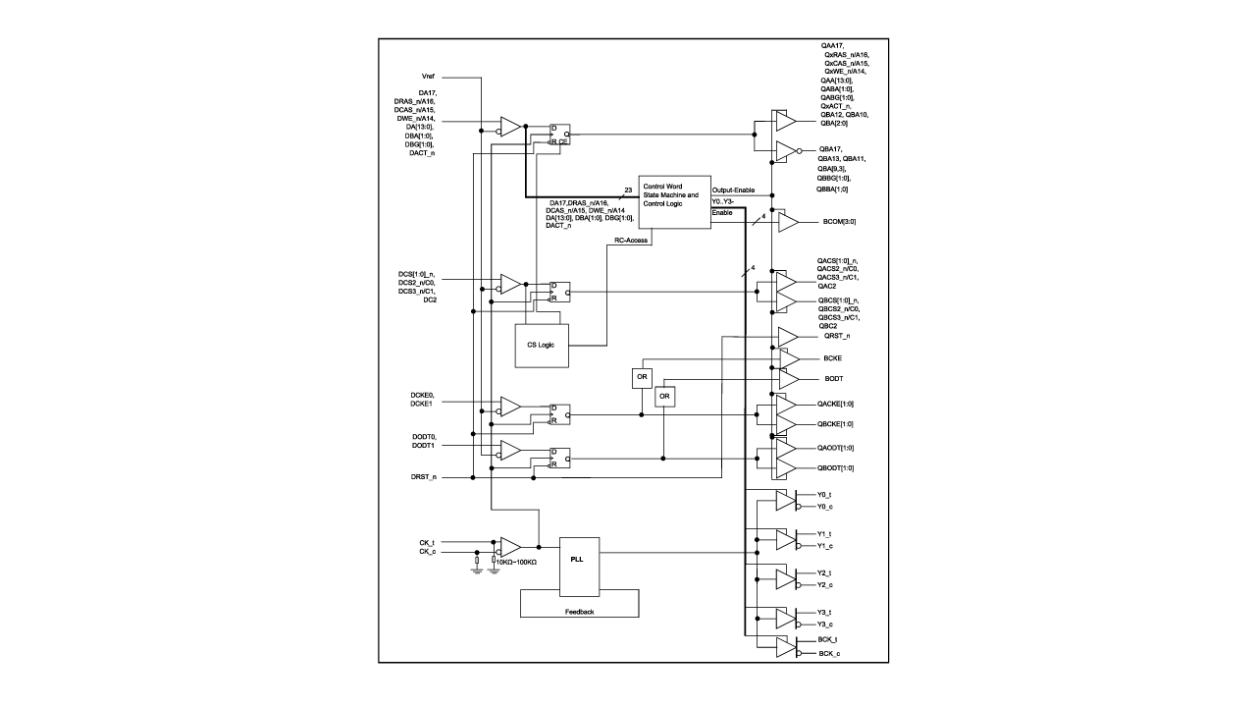

The JEDEC-compliant 4RCD0232K is a Gen 2.5 DDR4 registered clock driver (RCD) for enterprise-class server RDIMMs, LRDIMMs, and UDIMMs operating with a 1.2V supply.

产品参数

| 属性 | 值 |

|---|---|

| Function | Register + PLL |

| Supply Voltage (V) | 1.2 - 1.2 |

| SDRAM Type | DDR4 up to 3200 |

封装选项

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| FCCSP | 13.5 x 8.0 x 1.4 | 253 | 0.65 |

当前筛选条件