特性

- Integrated terminations provide differential Zo = 100Ω: reduced component count and board space

- 1.8V operation: minimal power consumption

- OE# pins: support DIF power management

- HCSL compatible differential input: can be driven by common clock sources

- LP-HCSL differential clock outputs: reduced power and board space

- Programmable Slew rate for each output: allows tuning for various line lengths

- Programmable output amplitude: allows tuning for various application environments.

- Pin/Software selectable PLL bandwidth and PLL bypass: minimize phase jitter for each application

- Outputs blocked until PLL is locked: clean system start-up

- Software selectable 50MHz or 125MHz PLL operation: useful for Ethernet applications

- Configuration can be accomplished with strapping pins: SMBus interface is not required for device control

- 3.3V tolerant SMBus interface works with legacy controllers

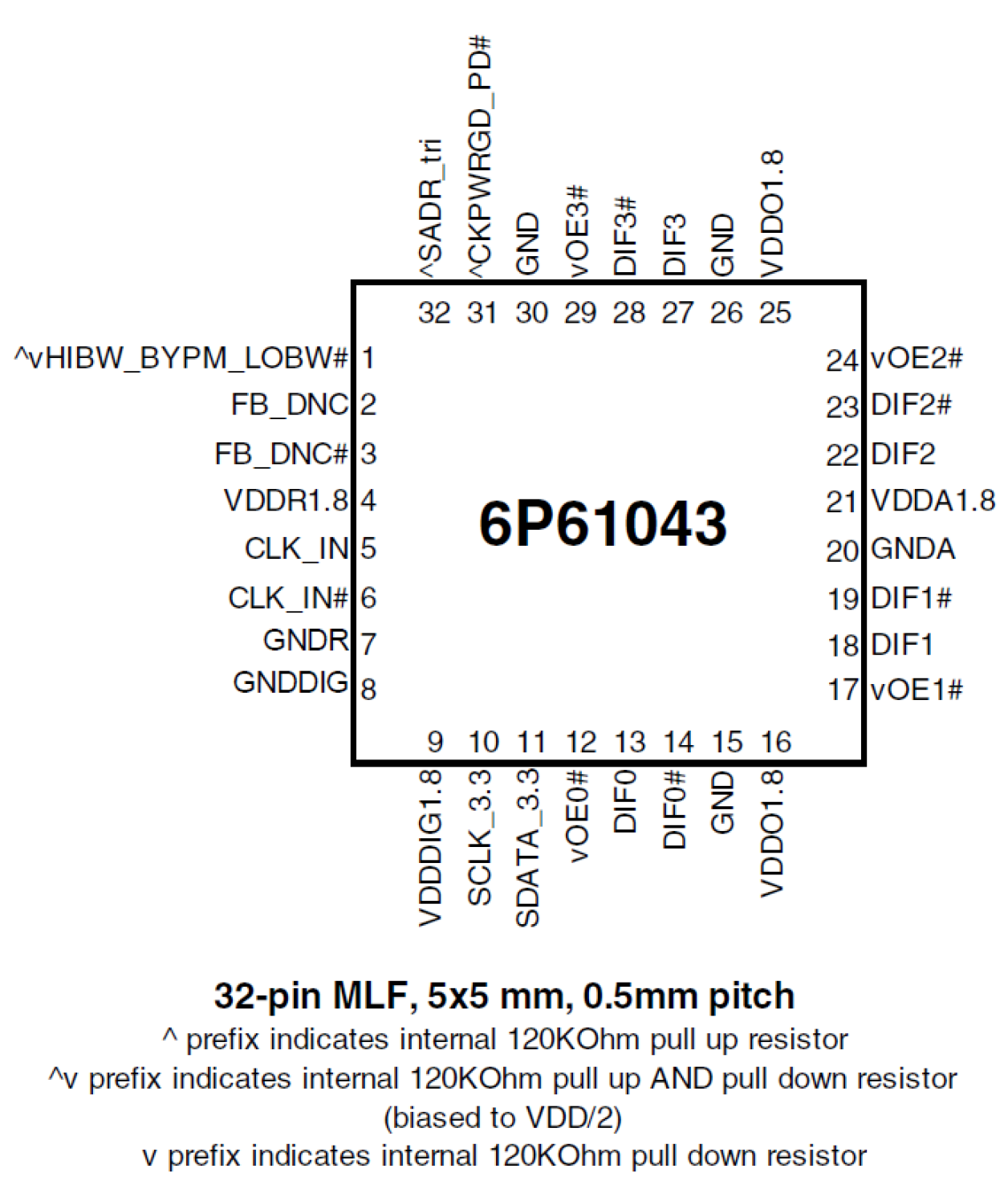

- Space saving 32-pin 5mm x 5mm MLF: minimal board space

- Selectable SMBus addresses: multiple devices can easily share an SMBus segment

描述

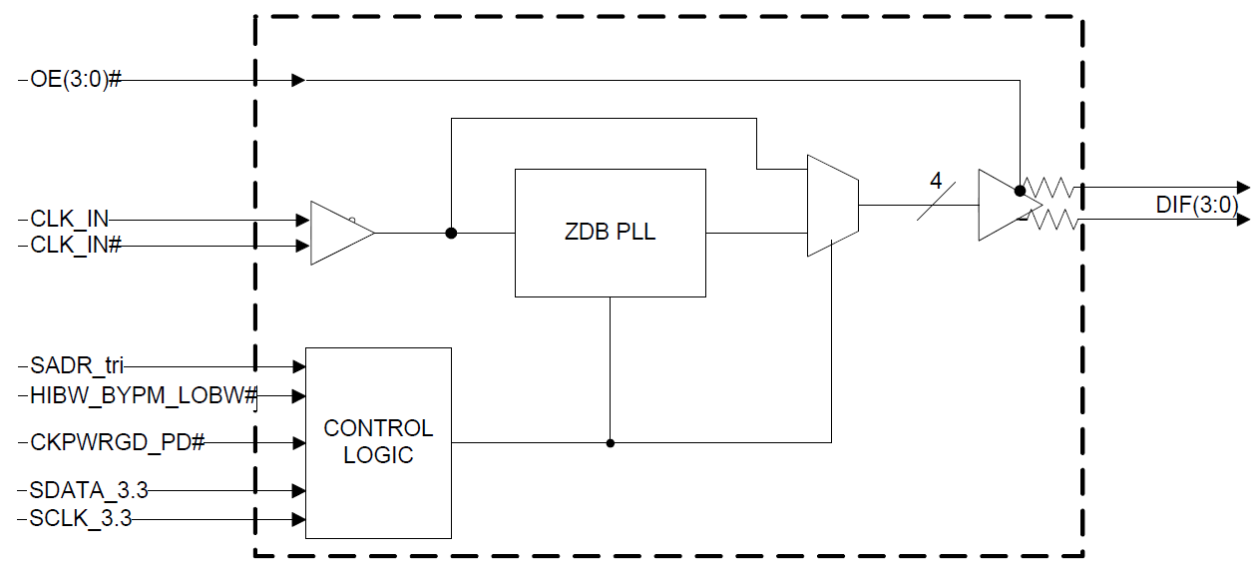

The 6P61043 is a 4-output very-low power buffer for 100MHz PCIe Gen 1, Gen 2, and Gen 3 applications with integrated output terminations providing Zo = 100Ω for Freescale Systems. The device has four output enables for clock management and three selectable SMBus addresses.

当前筛选条件