封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | PLCC |

| Pkg. Code: | PL52 |

| Lead Count (#): | 52 |

| Pkg. Dimensions (mm): | 19.0 x 19.0 x 3.63 |

| Pitch (mm): | 1.27 |

环境和出口类别

| Pb (Lead) Free | No |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 52 |

| Pb (Lead) Free | No |

| Carrier Type | Tube |

| Access Time (ns) | 35 |

| Architecture | Dual-Port |

| Bus Width (bits) | 9 |

| Core Voltage (V) | 5 |

| Density (Kb) | 18 |

| Function | Busy, Interrupt, Slave |

| I/O Type | 5.0 V TTL |

| Interface | Async |

| Length (mm) | 19 |

| MOQ | 48 |

| Moisture Sensitivity Level (MSL) | 3 |

| Organization | 2K x 9 |

| Package Area (mm²) | 361 |

| Pb Free Category | e0 |

| Pitch (mm) | 1.27 |

| Pkg. Dimensions (mm) | 19.0 x 19.0 x 3.63 |

| Pkg. Type | PLCC |

| Qty. per Carrier (#) | 24 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 3.63 |

| Width (mm) | 19 |

| 已发布 | No |

有关 70125 的资源

描述

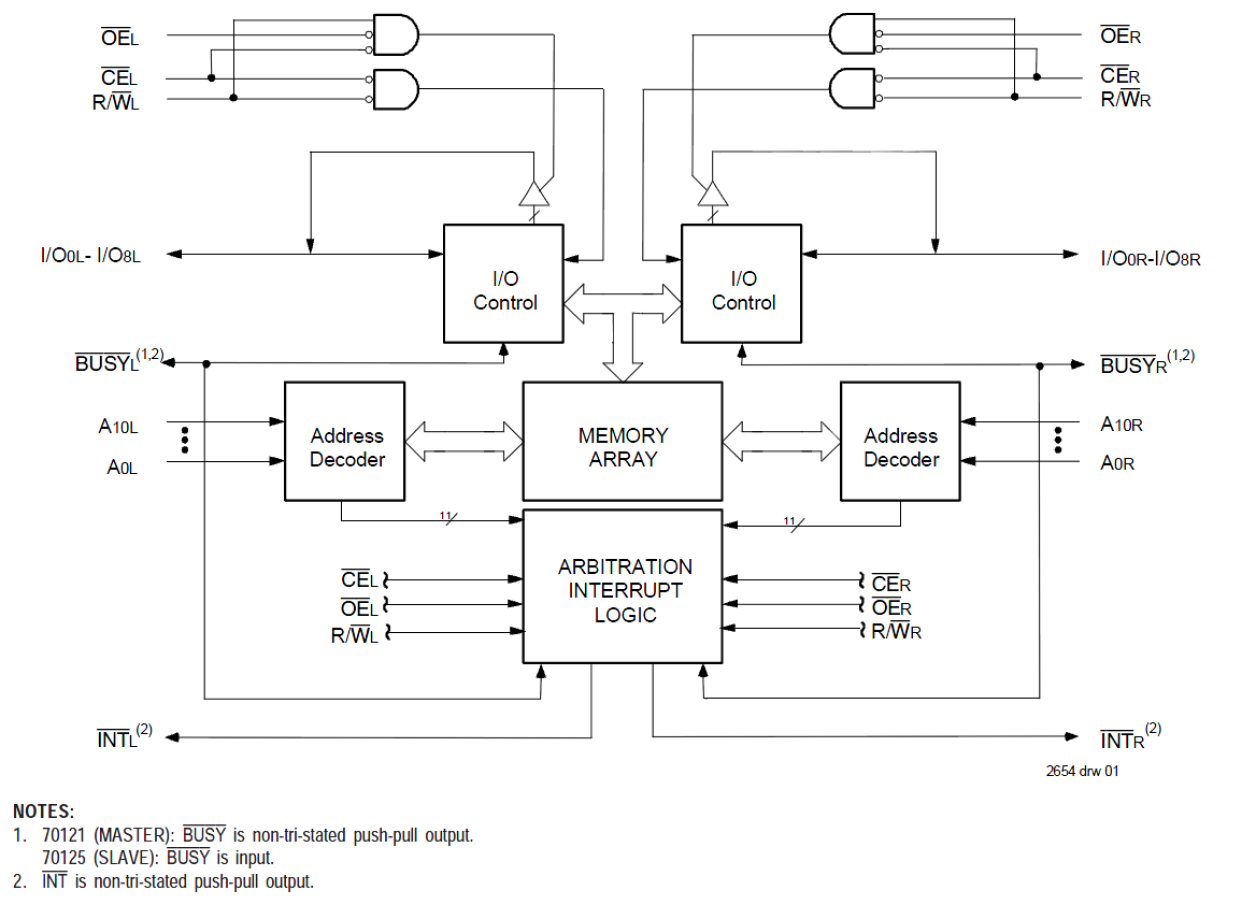

The 70125 is a high-speed 2K x 9 Dual-Port Static RAM designed to be used as a "SLAVE" Dual-Port together with the 70121 "MASTER" in 18-bit-or-more word width systems. Using the IDT MASTER/SLAVE Dual-Port RAM approach in 18-bit-or-wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic. An automatic power-down feature, controlled by CE, permits the on-chip circuitry of each port to enter a very low standby power mode.