封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TQFP |

| Pkg. Code: | PKG100 |

| Lead Count (#): | 100 |

| Pkg. Dimensions (mm): | 20.0 x 14.0 x 1.4 |

| Pitch (mm): | 0.65 |

环境和出口类别

| Pb (Lead) Free | Yes |

| ECCN (US) | 3A991.b.2.a |

| HTS (US) | 8542.32.0041 |

| Moisture Sensitivity Level (MSL) | 3 |

产品属性

| Lead Count (#) | 100 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tray |

| Architecture | ZBT |

| Bus Width (bits) | 36 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 4608 |

| I/O Frequency (MHz) | 100 - 100 |

| I/O Voltage (V) | 2.5 - 2.5 |

| Length (mm) | 20 |

| MOQ | 144 |

| Moisture Sensitivity Level (MSL) | 3 |

| Organization | 128K x 36 |

| Output Type | Pipelined |

| Package Area (mm²) | 280 |

| Pb Free Category | e3 Sn |

| Pitch (mm) | 0.65 |

| Pkg. Dimensions (mm) | 20.0 x 14.0 x 1.4 |

| Pkg. Type | TQFP |

| Qty. per Carrier (#) | 72 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.4 |

| Width (mm) | 14 |

有关 71V2546 的资源

描述

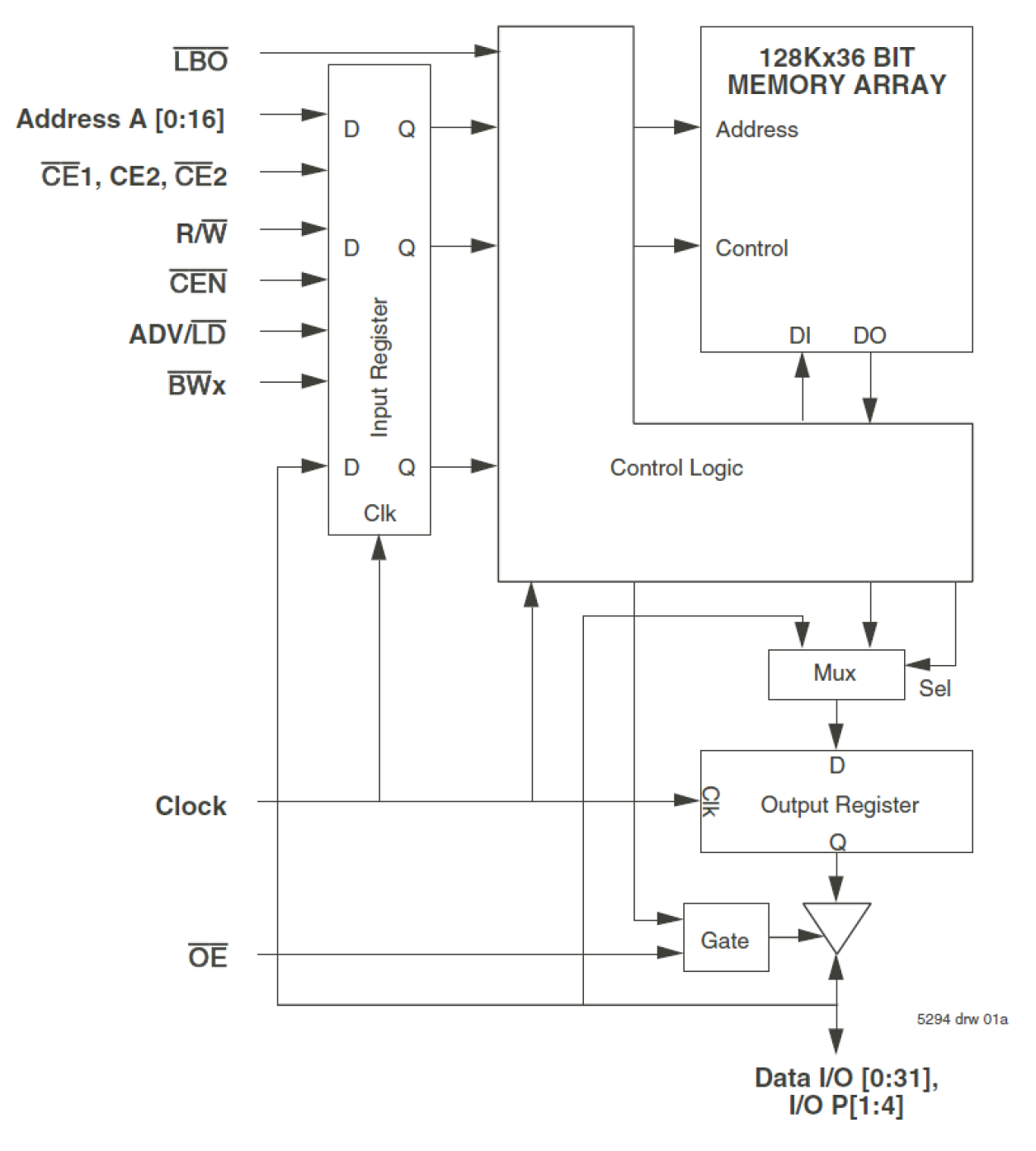

The 71V2546 3.3V CMOS Synchronous SRAM is organized as 128K x 36. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Thus, it has been given the name ZBTTM, or Zero Bus Turnaround. The 71V2546 has an on-chip burst counter. In the burst mode, it can provide four cycles of data for a single address presented to the SRAM.