特性

- Pin and functionally compatible with 720X family

- Low power consumption

- Ultra high speed—12ns access time

- Asynchronous and simultaneous read and write

- Fully expandable by both word depth and/or bit width

- Status Flags: Empty, Half-Full, Full

- Auto-retransmit capability

- MIL-STD-883, Class B available in 28 pin (300 & 600 mil) Cerdip package

- Industrial temperature range (–40C to +85C) is available

- Available in 28 pin SOIC, PDIP (300 & 600 mil), and 32 pin PLCC packages

描述

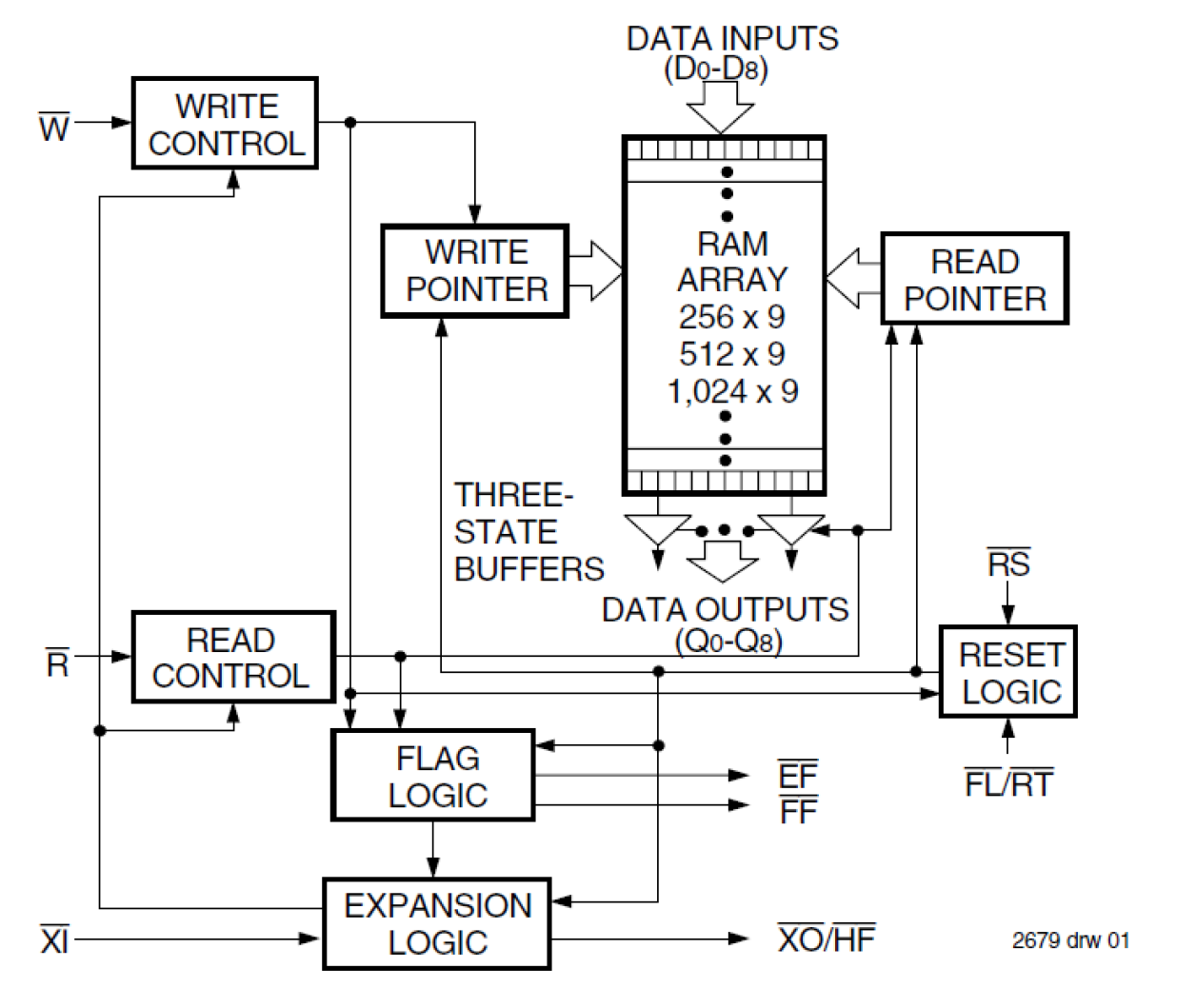

The 7202 is a 1K x 9 dual-port FIFO memory that loads and empties data on a first-in/first-out basis. The device uses Full and Empty flags to prevent data overflow and underflow. It has a Retransmit (RT) capability that allows for reset of the read pointer to its initial position when RT is pulsed LOW. It is designed for those applications requiring asynchronous and simultaneous read/writes in multiprocessing and rate buffer applications.

产品参数

| 属性 | 值 |

|---|---|

| Core Voltage (V) | 5 |

| Bus Width (bits) | 9 |

| Density (Kb) | 9 |

| Pkg. Code | PEG28, PLG32 |

| Interface | Asynchronous |

| I/O Type | 5.0 V TTL |

| Organization | 1K x 9 |

| Temp. Range (°C) | -40 to 85°C, 0 to 70°C |

| Architecture | Uni-directional |

| Access Time (ns) | 12, 15, 50 |

当前筛选条件