特性

- Equivalent to two 7202 1K x 9 FIFOs

- Asynchronous and simultaneous read and write

- Status Flags: Empty, Half-Full, Full

- Auto-retransmit capability

- Available in 56 pin TSSOP

- Industrial temperature range (–40C to +85C) is available

描述

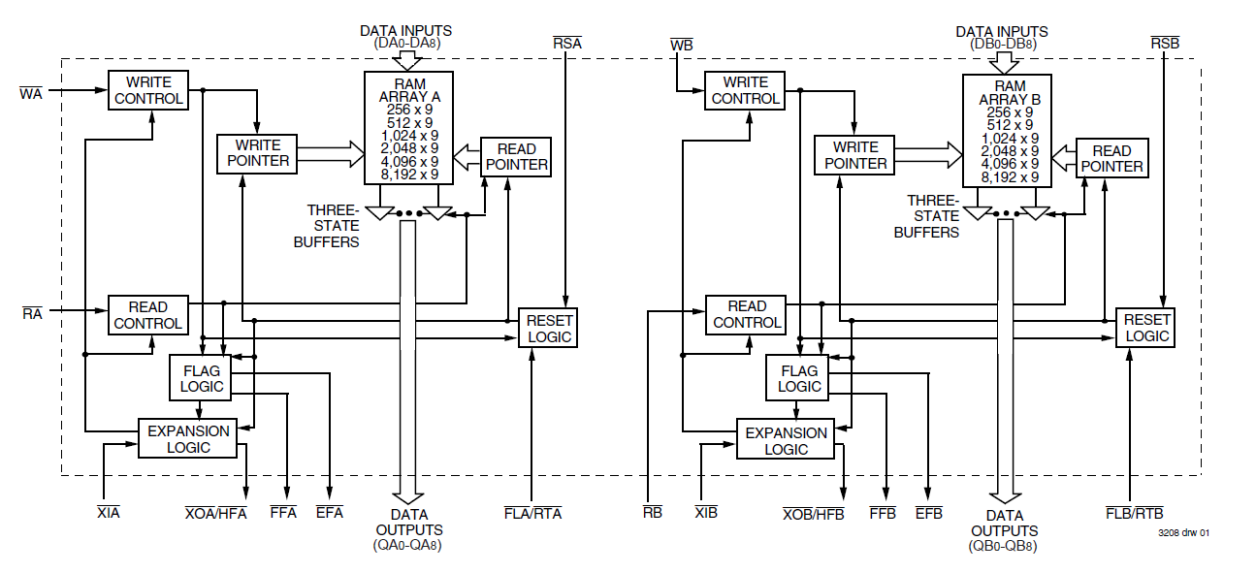

The 7282 is a dual-FIFO memory that loads and empties data on a first-in/first-out basis. It utilizes a 9-bit wide data array to allow for control and parity bits at the user's option. This is useful in data communications applications where a parity bit is needed for transmission/reception error checking. It is designed for those applications requiring asynchronous and simultaneous read/writes in multiprocessing and rate buffer applications.

当前筛选条件