封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | TSSOP |

| Pkg. Code: | PA56 |

| Lead Count (#): | 56 |

| Pkg. Dimensions (mm): | 14.0 x 6.1 x 1.0 |

| Pitch (mm): | 0.5 |

环境和出口类别

| Pb (Lead) Free | No |

| Moisture Sensitivity Level (MSL) | 1 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Lead Count (#) | 56 |

| Pb (Lead) Free | No |

| Carrier Type | Tube |

| Access Time (ns) | 20 |

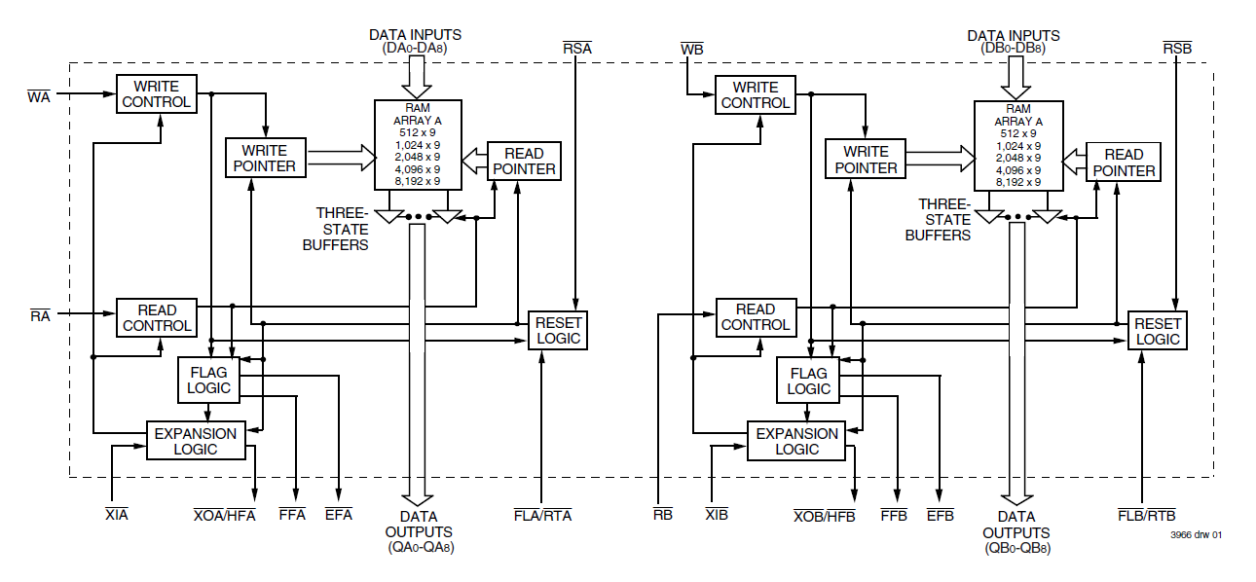

| Architecture | Dual FIFO |

| Bus Width (bits) | 9 |

| Core Voltage (V) | 3.3 |

| Density (Kb) | 9 |

| Family Name | DualAsync |

| I/O Type | 3.3 V LVTTL |

| Interface | Asynchronous |

| Length (mm) | 14 |

| MOQ | 238 |

| Moisture Sensitivity Level (MSL) | 1 |

| Organization | 1K x 9 |

| Package Area (mm²) | 85.4 |

| Pb Free Category | e0 |

| Pitch (mm) | 0.5 |

| Pkg. Dimensions (mm) | 14.0 x 6.1 x 1.0 |

| Pkg. Type | TSSOP |

| Qty. per Carrier (#) | 34 |

| Qty. per Reel (#) | 0 |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Tape & Reel | No |

| Temp. Range (°C) | -40 to 85°C |

| Thickness (mm) | 1 |

| Width (mm) | 6.1 |

有关 72V82 的资源

描述

The 72V82 is a dual-FIFO memory that loads and empties data on a first-in/first-out basis. It utilizes a 9-bit wide data array to allow for control and parity bits at the user's option. This is useful in data communications applications where a parity bit is needed for transmission/reception error checking. It is designed for those applications requiring asynchronous and simultaneous read/writes in multiprocessing and rate buffer applications.