封装信息

| CAD 模型: | View CAD Model |

| Pkg. Type: | CABGA |

| Pkg. Code: | AUG196 |

| Lead Count (#): | 196 |

| Pkg. Dimensions (mm): | 15.0 x 15.0 x 1.68 |

| Pitch (mm): | 1 |

环境和出口类别

| Pb (Lead) Free | Yes |

| Moisture Sensitivity Level (MSL) | 3 |

| ECCN (US) | |

| HTS (US) |

产品属性

| Pkg. Type | CABGA |

| Lead Count (#) | 196 |

| Pb (Lead) Free | Yes |

| Carrier Type | Tray |

| Advanced Features | Hitless Reference Switching, External Sync Input, VCXO-based APLL |

| App Jitter Compliance | GR-1244-CORE, GR-253-CORE, ITU-T G.812, ITU-T G.8262. ITU-T G.813, ITU-T G.783, Stratum 3, Stratum 4E, Stratum 4, SMC, EEC-Option 1, EEC-Option 2 Clocks |

| Application | Port Synchronizer |

| Channels (#) | 2 |

| Core Voltage (V) | 3.3 |

| Diff. Inputs | 4 |

| Diff. Outputs | 4 |

| Input Freq (MHz) | 1.0E-6 - 644.531 |

| Input Freq Range Type | TDM, DS1, E1, SONET/SDH, Ethernet, Sync Pulse |

| Input Type | LVPECL, LVDS, LVCMOS |

| Inputs (#) | 8 |

| Length (mm) | 15 |

| Loop Bandwidth Range (Hz) | 18 - 35 |

| MOQ | 126 |

| Moisture Sensitivity Level (MSL) | 3 |

| Output Banks (#) | 11 |

| Output Freq Range (MHz) | 1.0E-6 - 644.531 |

| Output Freq Range Type | 1PPS (1 Hz), TDM, DS1, E1, DS2, E3, DS3, 100BASE-T, STM-1/OC-3, STM-4/OC-12, 1000BASE-T/X, STM-16/OC-48, STM-64/OC-192/10GBASE-W, 10GBASE-R, XGMII/XAUI |

| Output Skew (ps) | 150 |

| Output Type | LVPECL, LVDS, LVCMOS |

| Output Voltage (V) | 3.3 |

| Outputs (#) | 11 |

| Package Area (mm²) | 225 |

| Pb Free Category | e1 SnAgCu |

| Phase Jitter Typ RMS (ps) | 0.23 |

| Pitch (mm) | 1 |

| Pkg. Dimensions (mm) | 15.0 x 15.0 x 1.68 |

| Price (USD) | $44.2388 |

| Prog. Clock | Yes |

| Prog. Interface | I2C, Serial, JTAG |

| Qty. per Carrier (#) | 126 |

| Qty. per Reel (#) | 0 |

| Reference Output | Yes |

| Requires Terms and Conditions | Does not require acceptance of Terms and Conditions |

| Spread Spectrum | No |

| Tape & Reel | No |

| Temp. Range (°C) | 0 to 70°C |

| Thickness (mm) | 1.68 |

| Width (mm) | 15 |

| Xtal Freq (KHz) | 12800 - 12800, 24883.2 - 24883.2, 25000 - 25000, 25781.2 - 25781.2 |

有关 82V3911 的资源

描述

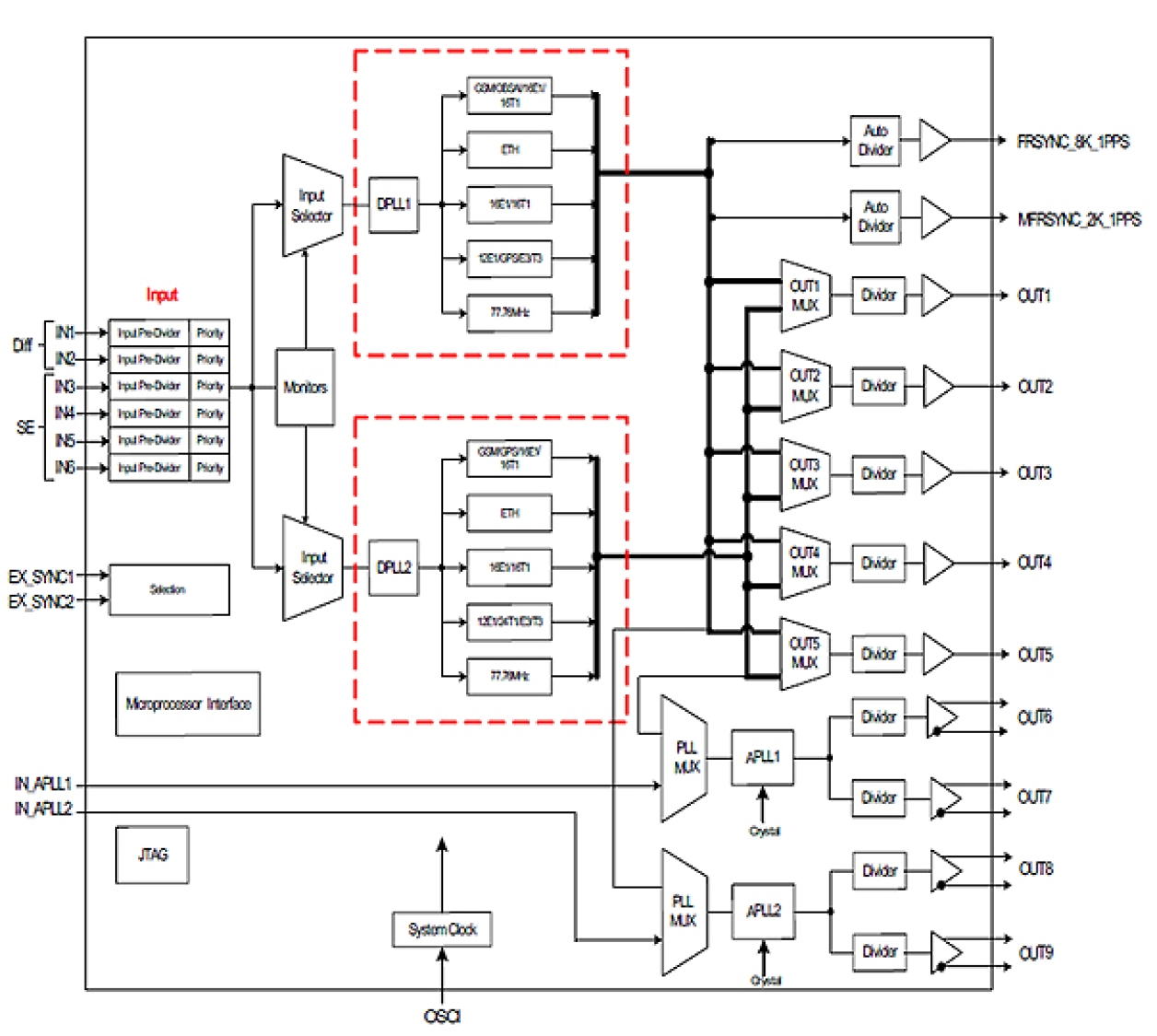

The 82V3911 is a single-chip, two-channel Synchronous Ethernet (SyncE) PLL. The device supports ITU-T G.8262, G.813, and Telcordia GR-253-CORE compliance with hitless reference switching, frequency translation, and jitter attenuation. Its ultra-low jitter generation makes it suitable for timing 10GBASE-R, 10GBASE-W, OC-192/STM-64, or 40GBASE-R PHYs.

The high-integration architecture minimizes component count and board space by including two independent digital PLLs (DPLLs); one for the transmit PHY function and one to provide recovered line timing to the system’s synchronous equipment timing source (SETS). Two independent jitter attenuating analog PLLs (APLLs) are also integrated; these APLLs generate clocks with jitter below 0.3ps RMS over the 10kHz to 20MHz integration range and can be used to directly time 10GbE or 40GbE network PHYs or other high-speed interfaces.

The DPLLs lock to a wide variety of telecom and Ethernet reference frequencies and suppress reference switching transients to generate highly reliable output clocks for optimal network performance. The 82V3911 offers a network PHY timing solution optimized for use in Ethernet switches, routers, multi-service switching platforms, wireless backhaul equipment, and other communications infrastructure. The device is available in a 196-ball 15mm x 15mm CABGA package and supports the standard industrial temperature range from -40 °C to +85 °C.