特性

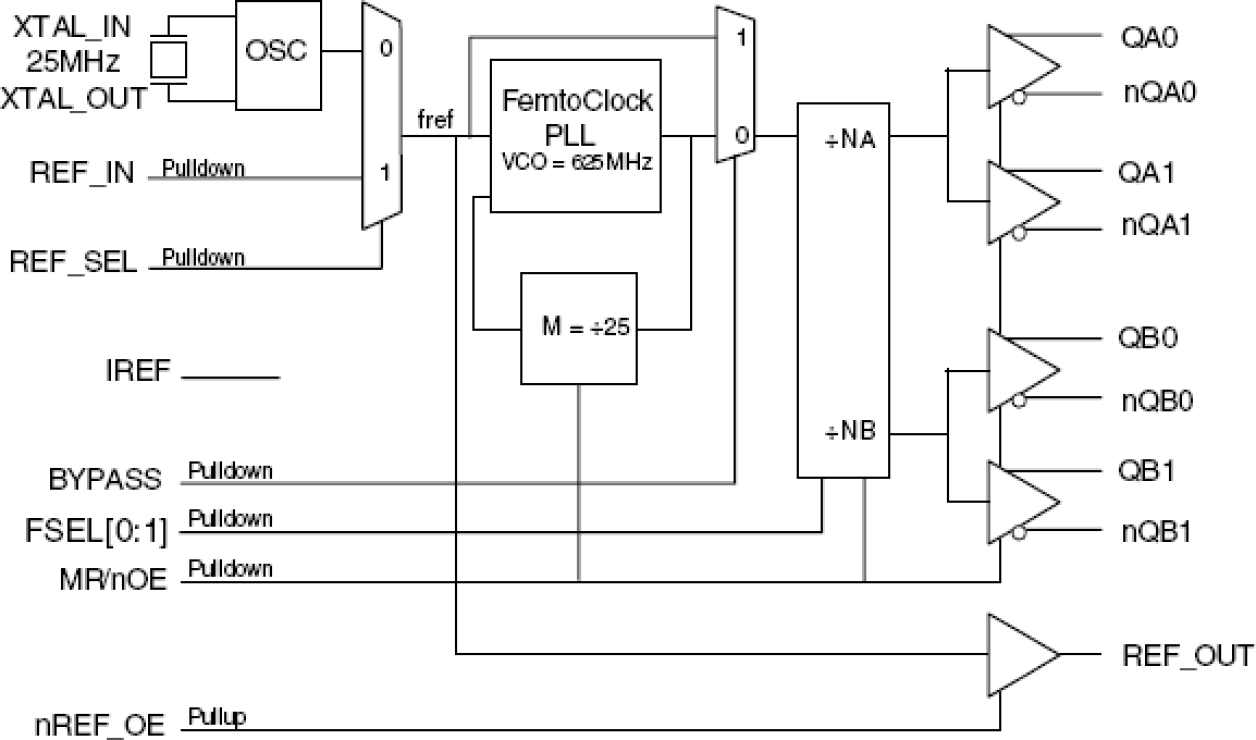

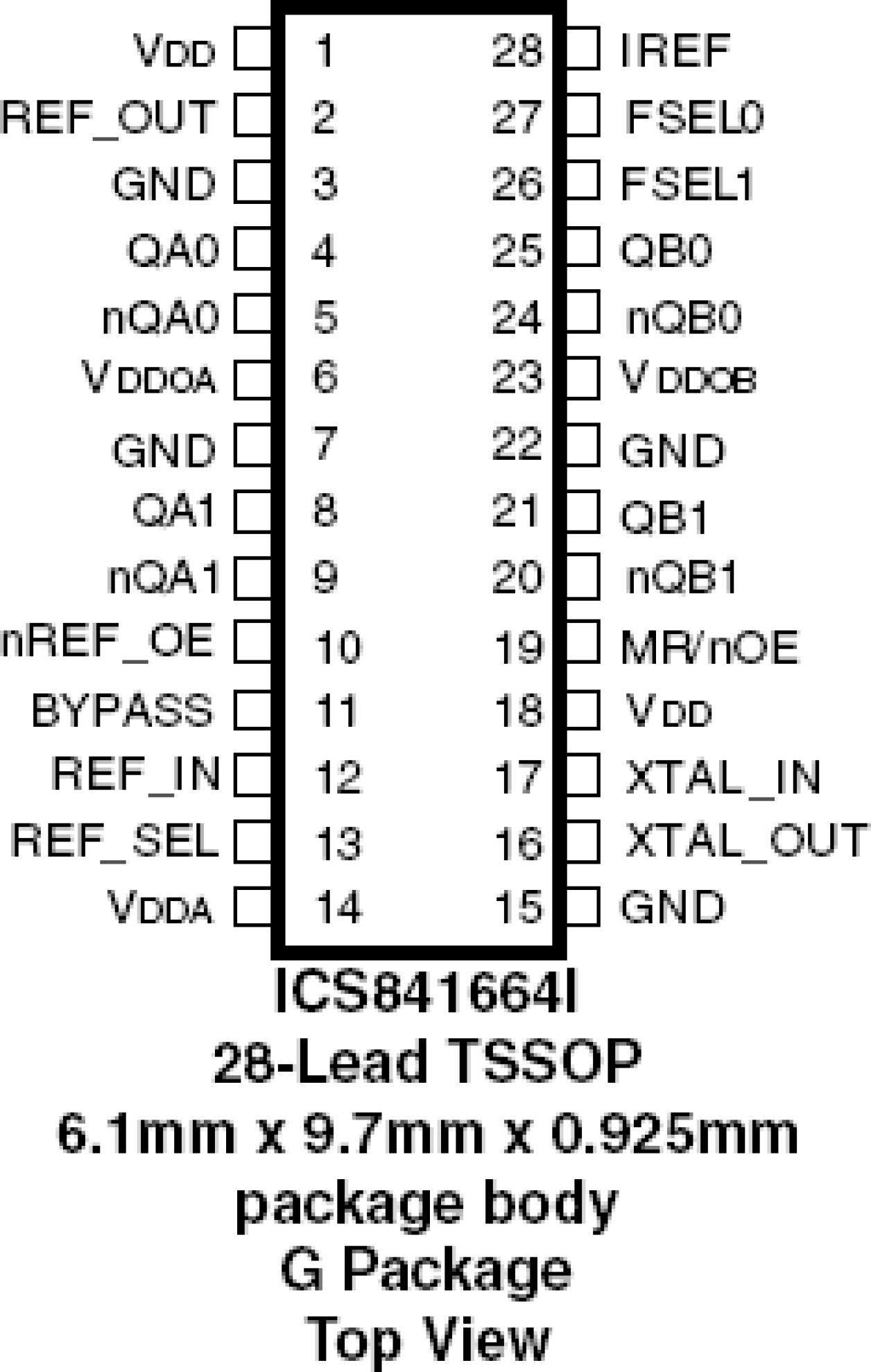

- Four differential HCSL clock outputs: configurable for sRIO (125MHz or 156.25MHz) clock signals One REF_OUT LVCMOS/LVTTL clock output

- Selectable crystal oscillator interface, 25MHz, 18pF parallel resonant crystal or LVCMOS/LVTTL single-ended reference clock input or LVCMOS/LVTTL single-ended input

- Supports the following output frequencies: 125MHz or 156.25MHz

- VCO: 625MHz

- Supports PLL bypass and output enable functions

- RMS phase jitter, using a 25MHz crystal (1.875MHz - 20MHz): 0.45ps (typical) @ 125MHz

- Full 3.3V power supply mode

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

描述

The 841664I is an optimized sRIO clock generator. The device uses a 25MHz parallel crystal to generate 125MHz and 156.25MHz clock signals, replacing solution requiring multiple oscillator and fanout buffer solutions. The device has excellent phase jitter (< 1ps rms) suitable to clock components requiring precise and low-jitter sRIO clock signals. Designed for telecom, networking and industrial application, the 841664I can also drive the high-speed sRIO SerDes clock inputs of communication processors, DSPs, switches and bridges.

当前筛选条件