特性

- One 0.7V current mode differential HCSL output pair

- Crystal oscillator interface: 25MHz

- Output frequency: 100MHz

- RMS period jitter: 3ps (maximum)

- Cycle-to-cycle jitter: 35ps (maximum)

- I2C support with readback capabilities up to 400kHz

- Spread Spectrum for electromagnetic interference (EMI) reduction

- 3.3V operating supply mode

- 0°C to 70°C ambient operating temperature

- Available in lead-free (RoHS 6) package

描述

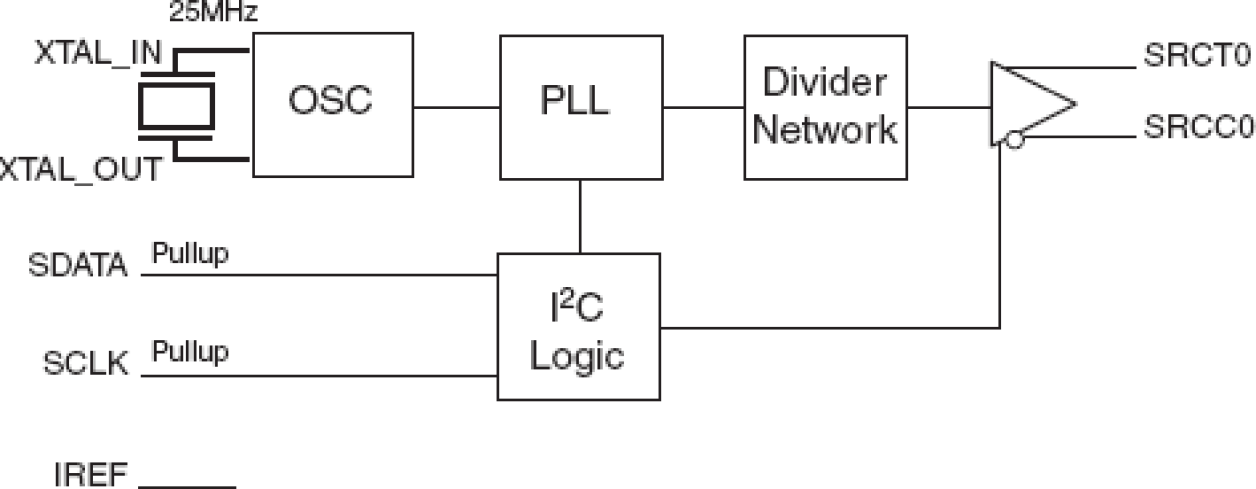

The 841S01 is a PLL-based clock generator specifically designed for PCI_Express™ Clock Generation applications. This device generates a 100MHz HCSL clock. The device offers a HCSL (Host Clock Signal Level) clock output from a clock input reference of 25MHz. The input reference may be derived from an external source or by the addition of a 25MHz crystal to the on-chip crystal oscillator. An external reference may be applied to the XTAL_IN pin with the XTAL_OUT pin left floating. The device offers spread spectrum clock output for reduced EMI applications. An I2C bus interface is used to enable or disable spread spectrum operation as well as select either a down spread value of -0.35% or -0.5%.

产品参数

| 属性 | 值 |

|---|---|

| Diff. Outputs | 1 |

| Diff. Output Signaling | HCSL |

| Output Freq Range (MHz) | 100 - 100 |

| Supply Voltage (V) | 3.3 - 3.3 |

| Output Type | HCSL |

| Package Area (mm²) | 22 |

| Battery Backup | No |

| Battery Seal | No |

| CPU Supervisory Function POR | No |

| Crystal Frequency Trimming | No |

| Frequency Out Pin | No |

| Inputs (#) | 1 |

| Input Freq (MHz) | 25 - 25 |

| Input Type | Crystal |

| Output Banks (#) | 1 |

| Core Voltage (V) | 3.3 |

| Output Voltage (V) | 3.3 |

| Product Category | PCI Express Clocks |

封装选项

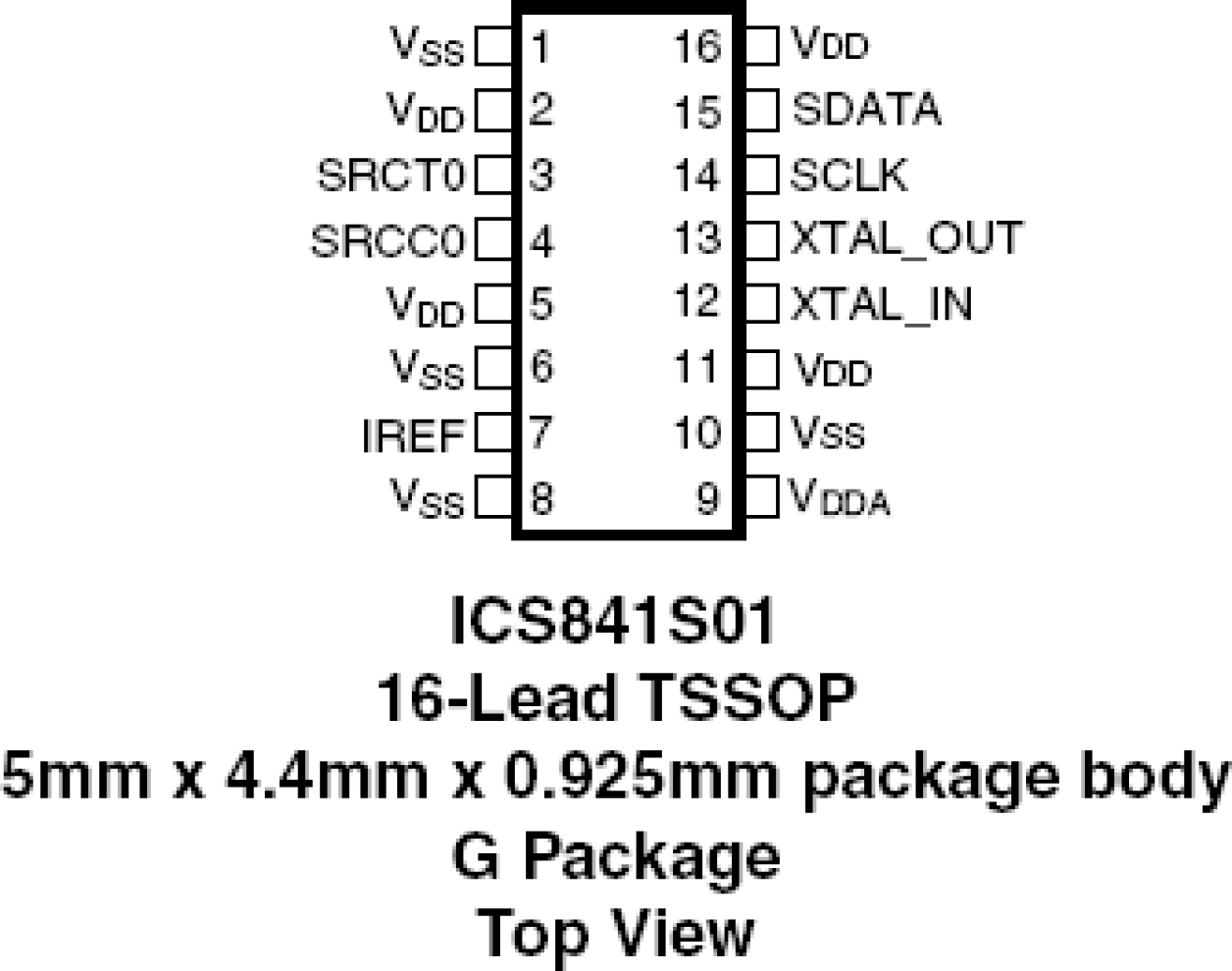

| Pkg. Type | Pkg. Dimensions (mm) | Lead Count (#) | Pitch (mm) |

|---|---|---|---|

| TSSOP | 5.0 x 4.4 x 1.0 | 16 | 0.65 |

当前筛选条件