特性

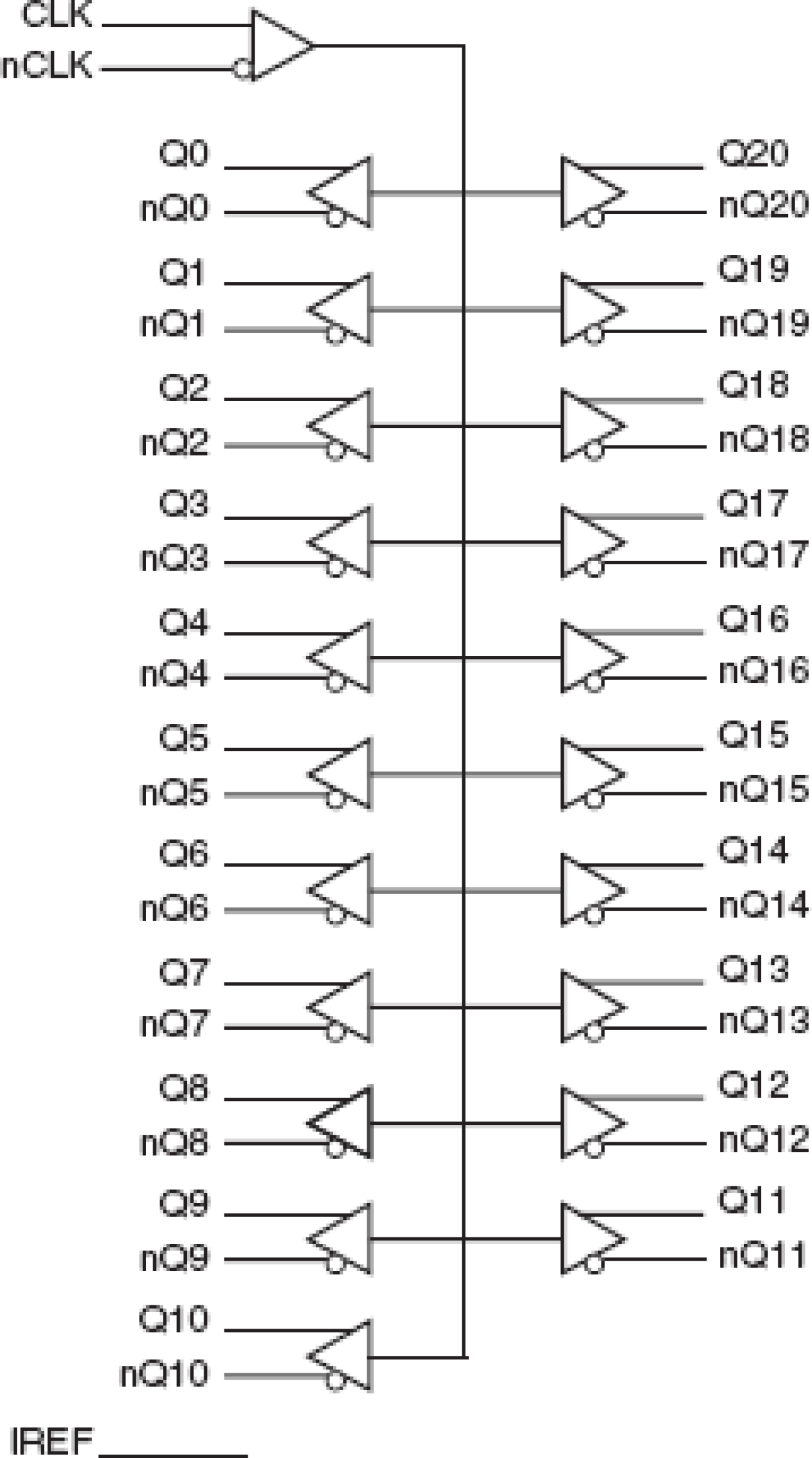

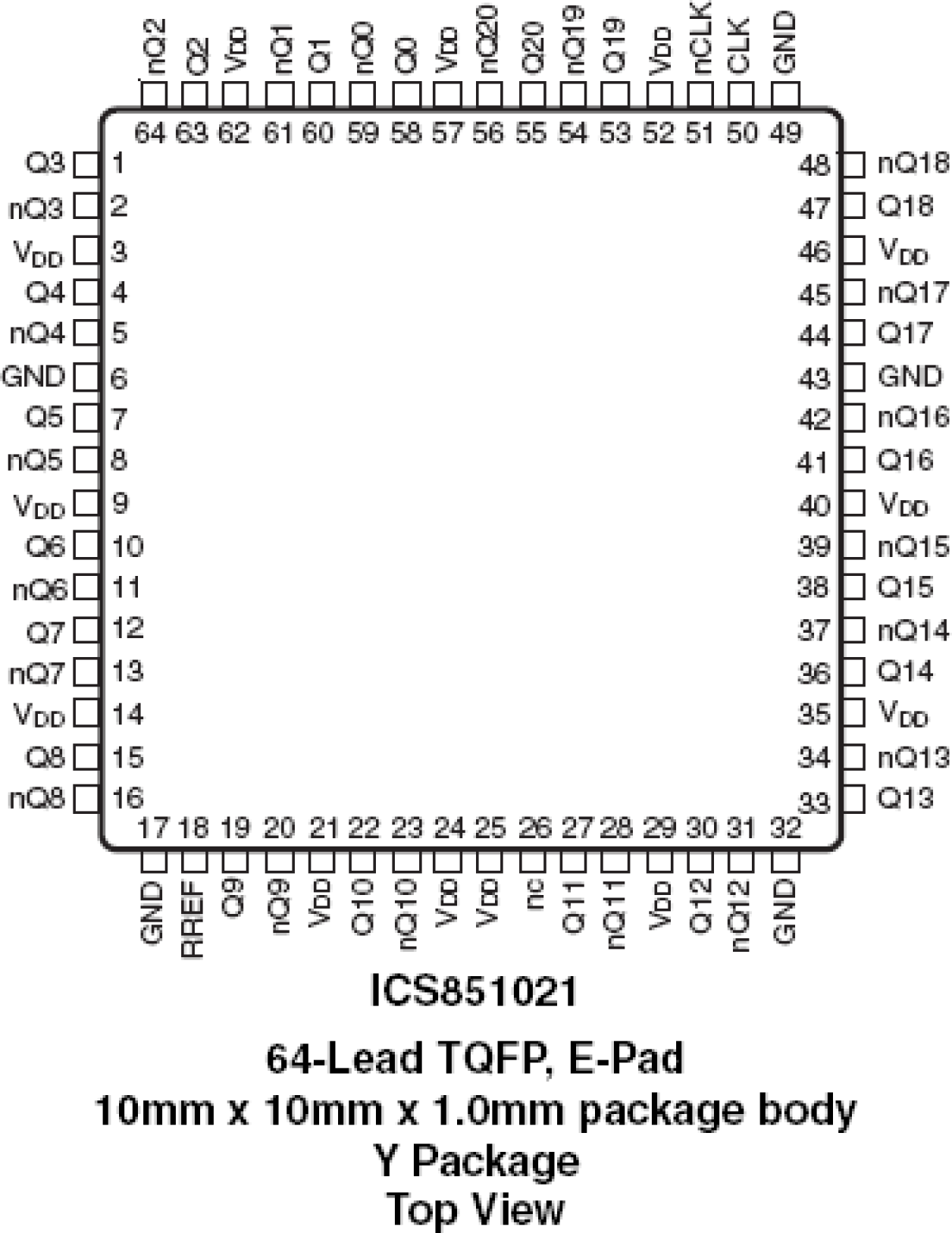

- Twenty-one differential HCSL outputs

- Translates any differential input signal (LVPECL, LVHSTL, LVDS, HCSL) to HCSL levels without external bias networks

- Maximum output frequency: 250MHz

- Output skew: 395ps (maximum)

- Part-to-part skew: 335ps (maximum)

- Output drift: 140ps (maximum)

- VOH: 850mV (maximum)

- Full 3.3V supply voltage

- Available in lead-free (RoHS 6) packages

- 0°C to 70°C ambient operating temperature

描述

The 851021 is a 1-to-21 Differential HCSL Fanout Buffer. The 851021 is designed to translate any differential signal levels to differential HCSL output levels. An external reference resistor is used to set the value of the current supplied to an external load/termination resistor. The load resistor value is chosen to equal the value of the characteristic line impedance of 50 ohms. The 851021 is characterized at an operating supply voltage of 3.3V. The differential HCSL outputs, accurate crossover voltage and duty cycle make the 851021 ideal for interfacing to PCI Express® and FBDIMM applications.

当前筛选条件